- PCIx

-

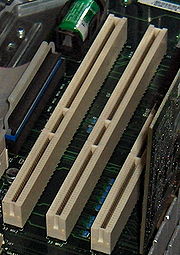

Ein PCI-Steckplatz (32 Bit)

Ein PCI-Steckplatz (32 Bit)Peripheral Component Interconnect, meist PCI abgekürzt, ist ein Bus-Standard zur Verbindung von Peripheriegeräten mit dem Chipsatz eines Prozessors.

Übersicht

Es gibt verschiedene Varianten und Einsatzgebiete des Standards (PC, Industrie, Telekommunikation). Die bekannteste Variante kommt hauptsächlich im PC-Umfeld zum Einsatz und heißt offiziell PCI Conventional. Praktisch jeder seit ca. 1994 gebaute IBM-PC-kompatible Computer ist mit meist zwei bis sieben Steckplätzen für PCI-Karten ausgerüstet (ausgenommen Miniatur- und mobile Versionen). Auch neuere Computer von Apple (von 1995 bis 2005, später dann PCI-Express) und Workstations von Sun besitzen einen PCI-Bus. In die Steckplätze kann eine große Anzahl verschiedener Karten diverser Hersteller eingesetzt werden. Unter anderem Netzwerkkarten, Modems, Soundkarten und (ältere oder Zweit-) Grafikkarten. Damit kann ein PC leicht an spezielle Bedürfnisse angepasst werden.

PCI-Netzwerkkarte

PCI-Netzwerkkarte

unten: die Kontakte für den Erweiterungsslot direkt auf der Leiterkarte

links: das genormte Blech mit der Anschlussbuchse. PCI-E und PCI Steckplätze auf einem Motherboard, von oben: PCI-E-4x, -16x, -1x, -16x und PCI

PCI-E und PCI Steckplätze auf einem Motherboard, von oben: PCI-E-4x, -16x, -1x, -16x und PCIVersion 1.0 des Standards wurde von Intel im Jahre 1991 definiert. Intel unterstützte den VESA Local Bus (VLB) nicht, da dieser speziell auf die 486-Architektur zugeschnitten war und weniger Durchsatz bot. Im Gegensatz dazu kann der PCI-Bus in jeder Architektur eingesetzt werden.

Mittlerweile existieren drei verschiedene Standards:

- Konventioneller PCI

- PCI 1.0, vorgeschlagen von Intel 1991

- PCI 2.0, eingeführt von PCI-SIG 1993

- PCI 2.1, beschlossen im Juni 1995

- PCI 2.2, beschlossen im Januar 1999

- PCI 2.3, beschlossen im März 2002

- PCI 3.0, beschlossen im April 2004

- PCI-Extended (PCI-X)

- PCI-X 1.0, beschlossen im September 1999

- PCI-X 2.0, beschlossen im Juli 2002

- PCI-Express (PCIe oder PCI-E)

- ursprünglich bekannt als 3GIO

- PCI-Express 1.0, beschlossen Juli 2002

- PCI Express 1.1

- PCI Express 2.0

Der PCI-Bus hat den ISA-Bus und den kurzlebigen VL-Bus, wie man sie in älteren PCs findet, ersetzt. Eine PCI-ISA-Bridge erlaubt jedoch die Anbindung des ISA-Busses an den PCI-Bus. Auf Systemen der Pentium-Generation und neuer, ist das die einzige Möglichkeit, ISA-Karten anzubinden da es sich beim ISA-Bus um den nach außen gelegten Systembus des Ur-PCs handelt. Der PCI-Bus erfüllte die Anforderungen für Grafik-, Netzwerk- und andere Schnittstellenkarten über längere Zeit.

Allerdings war er nach einiger Zeit nicht mehr schnell genug für die damals aufkommenden Grafikkarten mit 3D-Beschleunigung. 1997 etablierte man daher ein zusätzliches Bus-System, den Accelerated Graphics Port (AGP). Dieser baut ebenfalls auf dem PCI-Bus auf, ist jedoch als Punkt-zu-Punkt-Verbindung mit ergänzenden Seitenkanälen ausgeführt und wurde mittlerweile bis zum 8-fachen seiner ursprünglichen Übertragungsrate weiter entwickelt. Für so gut wie alle anderen Steckkarten-Typen blieb PCI dagegen bis heute Standard, wird aber seit 2005 schrittweise durch PCI-Express ersetzt (siehe unten).

Anders als der ISA-Bus ermöglicht PCI die dynamische Konfiguration eines Gerätes ohne Eingriff des Benutzers. Während des Bootvorgangs handeln das BIOS des PCI-Gerätes und das System-BIOS die Ressourcen aus, die das Gerät benötigt. Das erlaubt die Zuweisung von IRQs, Portadressen und Speicherbereichen entsprechend den lokalen Gegebenheiten. Bei ISA-Karten musste man häufig den zu verwendenden IRQ etc. per Steckbrücke manuell einstellen. Zusätzlich stellt der PCI-Bus dem Betriebssystem und anderen Programmen eine detaillierte Beschreibung aller verbundenen PCI-Geräte durch den PCI Configuration Space zur Verfügung.

Die PCI-Spezifikation regelt auch die physische Auslegung des Busses (u.a. den Abstand der Leiterbahnen zueinander), elektrische Eigenschaften, Timing und Protokolle. Die Geräte oder Schnittstellen müssen nicht unbedingt auf Steckkarten untergebracht werden, sondern können sich auch direkt auf der Hauptplatine des Computers befinden, die Spezifikation spricht hier von planar devices.

Allgemeine PCI-Bus-Spezifikationen

Der PCI-Bus ist ein synchroner Bus mit 33,33 MHz (= 30 ns pro Takt) oder nach Spezifikation 2.1 66,66 MHz Taktrate, also 15 ns pro Takt. Diese Werte sind Maximal-Werte, nach der Spezifikation kann der Takt auch niedriger und zudem variabel sein, beispielsweise zum Stromsparen. Deshalb hat der Bus eine Taktleitung. Alle Signale werden nur bei steigender Taktflanke übertragen(Single Data Rate). Die Signale können über CMOS-Treiber angesteuert werden, daher ist der gesamte Stromverbrauch relativ gering. Der Bus kann mit bis zu 10 Geräten bestückt werden, wobei zwischen Master (Herr) und Target (Ziel) unterschieden wird. Ein Master kann bei Bedarf selbst die Kontrolle über Abläufe auf dem Bus übernehmen, was vor allem für Karten mit hohem IO-Aufkommen, wie etwa Netzwerkkarten oder Festplatten-Controller, vorteilhaft ist. Als Geräte zählen auch auf der Hauptplatine untergebrachte Geräte, die Verbindung zum Host (PCI/Host-Schnittstelle) oder zu einem eventuell vorhandenen ISA-Bus (PCI/ISA-Schnittstelle) aufnehmen. Falls die Anzahl der Geräten nicht ausreicht, können über PCI/PCI-Schnittstellen (PCI-PCI-Bridge) weitere PCI-Busse in das System eingebunden werden.

Auf dem PCI-Bus kommuniziert immer ein Master mit einem Target. Die meisten PCI-Geräte können sowohl als Target angesprochen werden als auch als Master Transaktionen starten. Über einen Arbiter wird ein Master ausgewählt, der dann die Kontrolle über den Bus hat. Er beginnt einen Transfer, indem er eine Adresse an die 32 Daten/Adressleitungen und ein Kommando an 4 Kommando/Byte-Leitungen anlegt. Die Daten und Adressen werden über dieselben Leitungen übertragen und per Zeitmultiplexverfahren voneinander getrennt. Eine zusätzliche Paritätsleitung erlaubt das Erkennen von Fehlern.

CPU und Arbeitsspeicher sind über eine sogenannte Host-Bridge mit dem Bus verbunden. Die meisten Transaktionen auf dem Bus finden zwischen dieser Bridge und den restlichen Peripheriegeräten statt. Theoretisch können Peripheriegeräte auch untereinander kommunizieren, diese Möglichkeit wird jedoch nur sehr selten genutzt. Da Master-fähige Peripheriegeräte die Hostbridge als Target ansprechen können, sind sie in der Lage, direkt in den Arbeitsspeicher zu schreiben und aus ihm zu lesen - das entspricht Direct Memory Access (DMA).

Jedem Target werden beim Systemstart vom BIOS Adressbereiche zugeteilt. Über Herstellercodes können Karten nach dem Hochfahren eindeutig identifiziert werden. Über die Datenleitungen werden dann Daten übertragen, wobei die Kommando/Byte-Leitungen zur Auswahl der Bytes im 32-Bit-Wort dienen können. Dadurch sind neben 32-Bit auch 16- und 8-Bit Transfers möglich.

In der am weitesten verbreiteten PCI-Variante mit 32bit/33MHz können in jedem Takt maximal 32 Bit, also 4 Bytes übertragen werden, so dass die Transferrate maximal 133 MByte/s beträgt (4 Bytes in 30 ns). Über Ready-Leitungen kann sowohl der Master als auch das Target signalisieren, dass sie zur Aufnahme von Daten bereit sind. Falls Master oder Target nicht bereit sind, werden keine Daten übertragen, die Übertragung also verlangsamt.

Normalerweise beendet der Master den Datentransfer. Über ein STOP-Signal kann das Target ein Übertragungsende erzwingen. Ein anderer Master kann den Bus über REQ anfordern, wobei die derzeitige Übertragung nach einer vorgegebenen Latenzzeit beendet werden muss und der neue Master den Bus übernehmen kann.

Der PCI-Bus benötigt minimal 47 (Target) bzw. 49 (Master) Signale auf dem Bus. Ab der Version 2.1 der Spezifikation ist eine 64-Bit-Erweiterung definiert, die den Datenbus auf 64 Bit verbreitert. In einem System können 32-Bit- und 64-Bit-Geräte koexistieren und miteinander kommunizieren.

Auf dem Bus liegen vier Interruptleitungen, so dass jedes Gerät bis zu vier verschiedene Interrupts (INTA bis INTD) erzeugen kann. Die Interruptleitungen sind auf dem Bus aber nicht verbunden, sondern können einzeln geroutet und zugeordnet werden. Normalerweise wird nur INTA verwendet. Dieser kann jedoch je nach Steckplatz einem eigenen Interrupt zugeordnet werden oder, falls nicht genügend Interrupts vorhanden sind, zwischen verschiedenen Karten geteilt werden. Die Probleme des ISA-Busses, der oft zu wenig Interrupts zuordnen konnte, sind damit weitgehend Vergangenheit.PCI-Version PCI 2.0 PCI 32 bit 2.1 PCI 64 bit 2.1 PCI 2.2 PCI 2.3 PCI 3.0 Max. Busbreite (Bit) 32 32 64 64 64 64 Max. Taktrate (MHz) 33 66 66 66 66 66 Max. Datenrate‡ (GByte/s) 0,133 0,266 0,533 0,533 0,533 0,533 Max. Datenrate‡ (GBit/s) 1,066 2,133 4,266 4,266 4,266 4,266 Slots pro Bridge 4 4 2 2 2 2 Spannung (Volt) 5 5/3,3† 5/3,3† 5/3,3† 3,3 3,3 Einführung (Jahr) 1993 1994 1994 1999 2002 2004 †) 2.1 erlaubt 3,3V-Leitungen, 2.2 schreibt sie vor.

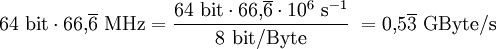

‡) Die max. Datenrate ist das Produkt aus max. Taktrate und max. Busbreite. Beispiel:

. (Beachte [Hz] = [s − 1].)

. (Beachte [Hz] = [s − 1].)

Der PCI Bus kann die angeschlossenen Geräte mit Strom versorgen. Laut Spezifikation beträgt die gelieferte Leistung pro Slot maximal 25 Watt. Je nach Spannung wurden unterschiedliche maximale Amperewerte festgelegt.[1]Spannung 3,3V +/-0.3V 5V +/-5% 12V +/-5% -12V +/-10% Stromstärke (pro Anschluss) max 6A max 5A 500mA 100mA PCI-Bus-Signale

Die Art der Ein- und Ausgänge lassen sich wie folgt einteilen:

Input in Normaler Eingang Output out Normaler Ausgang Tri-State t/s bidirektionaler Tri-State Ausgang Sustained-Tri-State s/t/s Low-aktiver Ausgang, der nur von einem Gerät getrieben werden darf. Setzt ein Gerät die Leitung auf low, so muss es, um die Leitung wieder freizugeben, die Leitung für mindestens einen Takt auf high setzen. Frühestens nach einem Takt, nachdem die Leitung freigegeben wurde, darf ein anderes Gerät die Leitung nutzen. Ein zentraler Pullup-Widerstand ist notwendig. Open-Drain o/d Low-aktiver Ausgang, fungiert als ODER-Verknüpfung mit anderen Geräten.Ein zentraler Pullup ist notwendig. Signal Art Beschreibung Systemsignale: CLK in Dient zur Synchronisation aller Komponenten. Die Taktfrequenz beträgt 33 MHz oder 66 MHz. Die Minimalfrequenz ist 0 MHz. RST# in Rücksetzen aller Systemkomponenten. Adress- und Datensignale: AD[31..0] t/s gemultiplexte Adress- und Datensignale C/BE[3..0]# t/s gemultiplexte Befehl- und Byte-Enable-Signale PAR t/s Die Parität für die Daten- und Adresssignale 0 bis 31, welche um einen Takt versetzt übertragen wird. Kontrollsignale: FRAME# s/t/s Dass eine Übertragung läuft, zeigt der Master mit FRAME# an. Wird die Übertragung der Daten beendet, nimmt der Master die Leitung zurück. Eine deaktivierte Leitung bedeutet, dass die Übertragung beendet wird oder beendet ist. IRDY# s/t/s Der Master zeigt mit Initiator Ready an, dass ein Wort übergeben oder übernommen werden kann. TRDY# s/t/s Der Target zeigt mit Target Ready an, dass ein Wort übergeben oder übernommen werden kann. STOP# s/t/s Der Target zeigt dem Master an, dass die Übertragung beendet werden soll. LOCK# s/t/s LOCK schützt einen Zugriff auf einen oder mehrere Target während der Übertragung vor der Benutzung anderer Master. IDSEL in Auswahl während der Konfigurationsphase DEVSEL# s/t/s Target hat Adresse erkannt Arbitrierung (nur Master): REQ# s/t/s Die Absicht eines Masters auf den Bus wird hiermit angezeigt.Dieses Signal ist eine Punkt-zu-Punkt-Verbindung von jedem Master zu einem zentralen Arbiter. GNT# in Erlaubt den Zugriff auf den Bus. Dieses Signal ist eine Punkt-zu-Punkt-Verbindung von einem zentralen Arbiter zu jedem Master. Fehlersignalisierung: PERR# s/t/s Einen Takt nach PAR zeigt dieses Signal einen Daten-Parity-Fehler (nicht bei einem Special-Cycle-Befehl) an. SERR# o/d System Error zeigt bei einem Special-Cycle-Befehl einen Daten- oder sonstigen Systemfehler an. Interrupt-Signale: INTA# o/d Ein Gerät mit einer Funktion zeigt einen Interrupt an. Ein Gerät mit mehr Funktionen zeigt einen Interrupt A an. INTB# o/d Ein Gerät mit mehr als einer Funktion zeigt einen Interrupt B an. INTC# o/d Ein Gerät mit mehr als einer Funktion zeigt einen Interrupt C an. INTD# o/d Ein Gerät mit mehr als einer Funktion zeigt einen Interrupt D an. Cache Signale (optional, in PCI 2.x als veraltet deklariert): SBO# inout Snoop Backoff zeigt einen „cache hit“ für eine modifizierte Cachezeile an. SDONE inout Snoop Done zeigt das Ende eines Snoops des aktuellen Zugriffs an. zusätzliche Signale: PRSNT[1..2]# out Zeigt das Vorhandensein einer Einsteckkarte und deren Energieverbrauch an. Mindestens eines der beiden Signale (also 3 verschiedene Kombinationen für 3 verschiedene Verbrauchsklassen) wird auf der Karte mit Masse verbunden und das eventuell andere bleibt offen. Diese Signale sind für jeden Slot individuell mit einem System-Chip verbunden und haben alle einen Pullup. Diese Signale sind nur bei Einsteckkarten vorhanden, bei On-Board-Peripherie gibt es diese nicht, da On-Board-Komponenten nicht austauschbar sind und der Stromverbrauch im Vorhinein bekannt ist. CLKRUN# o/d Kontrolliert die Abschaltung des CLK-Signals zu Stromsparzwecken. M66EN o/d Dieses Signal, das ursprünglich ein Massepin war, signalisiert die 66-MHz-Fähigkeit eines Geräts indem es unverbunden bleibt oder als Eingang beschaltet wird. Ältere oder langsame Geräte verlangsamen den gesamten Bus auf 33 MHz, indem sie das Signal mit Masse verbinden. 64-Bit Erweiterungssignale: D[63..32] t/s Die oberen 32 Bit der Datensignale. C/BE[7..4]# t/s Die oberen 4 Bit der Befehls- und Byte-Enable-Signale. REQ64# s/t/s Request64 zeigt die Absicht eines Masters für eine 64-Bit-Übertragung an. Dieses Signal ist eine Punkt-zu-Punkt Verbindung von einem zentralen Arbiter zu jedem Master. GNT64# in Grant64 erlaubt den Zugriff für eine 64-Bit-Übertragung.Dieses Signal ist eine Punkt-zu-Punkt Verbindung von einem zentralen Arbiter zu jedem Master. PAR64 t/s Parity64 über AD[63..32] und C/BE[7..4]# um einen Takt versetzt. JTAG-Signale: TCK in Test Clock TDI in Test Data In TDO out Test Data Out TMS in Test Mode Select TRST# in Test Reset Signale auf dem PCI-Bus - das #-Zeichen deutet an, dass die Signale Low Active sind.

PCI-ID

Jedes Gerät bzw. Steckkarte an einem PCI-Bus besitzt eine eindeutige Hardware-Kennung (ID). Diese setzt sich aus einem Teil für die Identifikation des Herstellers und einem Teil für das Modell zusammen.

Class-ID ':' Hersteller-ID ':' Geräte-ID

Beispielsweise:

0200:8086:10b5

Hierbei steht:

- 0200 für einen Ethernet Network Controller

- 8086 für die Intel Corporation (die Zahl ist zwar hexadezimal, aber die Ziffern würden bei Dezimalschreibweise für Intels Urvater der x86-Architektur stehen)

- 10b5 für das Gerät 82546GB Gigabit Ethernet Controller (Copper)

Über die Class-ID wird das Gerät einer bestimmten Gruppe zugeordnet. Das erleichtert die Ermittlung unbekannter Geräte.

Operationen auf dem PCI-Bus

Nach der Konfiguration aller Geräte durch das BIOS können alle Geräte über ein Befehlsprotokoll angesprochen werden. Dieses setzt sich aus dem Befehl, der Adresse und einer Folge von Daten zusammen.

C/BE3# C/BE2# C/BE1# C/BE0# Beschreibung 0 0 0 0 Der Interrupt Acknowledge Befehl ist ein implizierter Lesezugriff auf den System Interruptcontroller. Die „byte enable“-Bits geben dabei die Größe des Interruptvektors an. 0 0 0 1 Der Special Cycle Befehl ist für einfache Broadcast-Nachrichten (?) 0 0 1 0 Der I/O Read Befehl ist für das Lesen aus dem Speicher, der als I/O-Adressraum (engl. „address space“) eingebunden ist. 0 0 1 1 Der I/O Write Befehl ist für das Schreiben in den Speicher, der als I/O Adressraum (engl. „address space“) eingebunden ist. 0 1 0 0 Auf „Reserved“-Befehle dürfen PCI-Geräte nicht reagieren. 0 1 0 1 Reserviert 0 1 1 0 Der Memory Read-Befehl ist für das Lesen aus dem Speicher, der als „Memory Address Space“ eingebunden ist. 0 1 1 1 Der Memory Write-Befehl ist für das Schreiben in den Speicher, der als „Memory Address Space“ eingebunden ist. 1 0 0 0 Reserviert 1 0 0 1 Reserviert 1 0 1 0 Der Configuration Read-Befehl liest aus den internen Konfigurationsregistern (Configuration Space). 1 0 1 1 Der Configuration Write-Befehl schreibt in die internen Konfigurationsregister (Configuration Space). 1 1 0 0 Der Memory Read Multiple-Befehl liest mehr als eine Cachezeile aus dem Speicher. 1 1 0 1 Der Dual Address Cycle-Befehl erlaubt das Hintereinander-Senden von zwei 32-Bit-Adresszeilen, um einen 64-Bit-Adressbereich in einer 32-Bit-PCI-Umgebung ansprechen zu können. 1 1 1 0 Der Memory Read Line-Befehl liest eine Cachezeile aus dem Speicher. 1 1 1 1 Der Memory Write and Invalidate-Befehl schreibt mindestens eine ganze Cachezeile in den Speicher. Grundlegende PCI-Varianten

- PCI Conventional, erlaubt Busbreiten von 32 oder 64 Bit und Übertragungen mit 33 oder 66 MHz Takt (max. 528 MByte/s)

- PCI-X, 64-Bit-Version von PCI Conventional mit 66, 100 oder 133 MHz Takt (max. 1.066 MByte/s)

- PCI-X 266 (PCI-X DDR), PCI-X mit 266 MHz Nominaltakt (max. 2.133 MByte/s)

- Mini PCI, kleinere Bauform für Notebooks etc.

- CompactPCI, elektrisch voll PCI-kompatibel, jedoch in Form von Einschüben mit 3 bzw. 6 HE

- PCI Low-Profile, halbe Bauhöhe

- PC/104+ und PCI104 , voll PCI-kompatibel für Stapelcomputer

Abmessungen der PCI-Varianten

Standard Zoll Millimeter Maximale Höhe: 4.2″ 107mm Maximale Länge (kurze Karte): 6.875″ 175 mm Maximale Länge (lange Karte): 12.283″ 312 mm Low Profile Maximale Höhe: 2.536″ 64 mm Minimale Höhe: 0.945″ 24 mm Maximale Länge (kurze Karte) (MD1): 4.72″ 120 mm Maximale Länge (lange Karte) (MD2): 6.6″ 168 mm Kodierung der Kontaktleiste

- 3,3V-kompatible Karten haben eine Kerbe links (Richtung Slotblech)

- 5V-kompatible Karten haben eine Kerbe rechts

- Universal-Karten haben beide Kerben

- Slots nach PCI 2.x haben einen Steg rechts (die dem Slotblech abgewandte Seite). Die PCI 2.3-Spezifikation unterstützt zwar keine 5V-Karten mehr, diese passen aber dennoch physikalisch in den Slot.

- Slots nach PCI 3.0 haben einen Steg links (Richtung Slotblech), so dass nur noch 3,3V- und Universal-Karten mit der entsprechenden Kerbe eingesteckt werden können.

Andere PCI-Varianten

- PCI-Express (zuerst 3GIO genannt [Eingabe/Ausgabe der dritten Generation], Abkürzung PCIe oder PCI-E) ist im Gegensatz zum PCI-Bus auf der elektrischen Ebene eine serielle Punkt-zu-Punkt-Verbindung, die aber PCI-Signalisierung und -Programmiertechniken verwendet und daher von Betriebssystem und Software wie PCI behandelt werden kann. Seit 2004 ersetzt PCI-Express schrittweise sowohl PCI als auch AGP. Hardwaretechnisch ist es nicht kompatibel zu PCI oder AGP.

Powermanagement mit PCI

Die Energiesparfunktionen für den PCI-Bus sind Teil einer optional zu implementierenden Spezifikation, die zeitlich zwischen den PCI-Versionen 2.1 und 2.2 angesiedelt ist. Jedes PM-fähige Gerät hat ein zusätzliches 8 Byte langes Feld im Configuration Space, über das es mitteilen kann, welche Energiespar-Modi es unterstützt und entsprechend gesteuert werden kann. Jedes PCI-Gerät kann sich in einem von vier möglichen Operationsmodi befinden (D0-D3). Je höher die Nummer, desto weniger Energie verbraucht das Gerät. Auch wenn ein Gerät nichts von PCI-Powermanagement weiß, unterstützt es die Modi D0 und D3, da diese äquivalent zu an und aus sind. Ob und wieviel Energie in den dazwischen liegenden Modi gespart werden kann, liegt im Ermessen des Hardware-Herstellers. Ein Gerät kann aus einem bestimmten Modus in alle „darunter“ liegenden Modi wechseln, sowie aus jedem Modus in den Zustand D0.

Obwohl man Geräte durchaus manuell, während des laufenden Betriebes, in einen anderen Energiesparmodus bringen kann, wird man in den meisten Fällen mit Hilfe von APM oder ACPI einen globalen Energiesparmodus für den Computer setzen, der vom Powermanagement des Betriebssystems gesteuert wird. In den Modi D1 und D2 besteht für ein entsprechend ausgerüstetes PCI-Gerät die Möglichkeit, zu einem beliebigen Zeitpunkt ein so genanntes Power Management Event Signal (PME) auf den Bus zu legen, das dann an das Powermanagement des Betriebssystems weitergeleitet wird und dazu verwendet werden kann, das System auf Anforderung wieder global „aufzuwecken“, etwa wenn eine Netzwerkkarte einlaufende Daten erkennt, die behandelt werden müssen.

Begriffe

- Fast Back-to-Back: Wenn alle Geräte diesen Modus unterstützen, kann die IDLE-Phase zwischen zwei PCI-Zyklen entfallen. Das erhöht den Datendurchsatz auf dem Bus.

- Special Cycle: Über „Special Cycle“ können Rundrufnachrichten (Broadcast messages) an alle angeschlossenen Geräte gesendet werden.

- Address Space: einer von drei Adressbereichen - Memory, I/O oder Configuration Space

- Configuration Space: Der „Configuration Space“ ist ein Speicherbereich (256 bzw. 4096 Bytes) jedes PCI-Geräts, der zur Identifizierung und Konfiguration des Geräts dient. Der Configuration Space besteht aus einem standardisierten Kopf (Header) und zusätzlichen gerätespezifischen Daten wie beispielsweise Adressbereichen. Das BIOS bzw. der Treiber für ein PCI-Gerät kann anhand dieser Daten das Gerät passend konfigurieren.

Interessengruppen

Special Interest Group

1992 wurde die Spezielle Interessengruppe „PCI-SIG“ (ursprüngliche Bezeichnung: „Peripheral Component Interconnect Special Interest Group“) gegründet. Die Aufgabe der PCI-SIG ist die Verwaltung und die Weiterentwicklung des PCI-Standards. Bei PCI-SIG können Firmen und Organisationen Mitglied werden. Im Jahr 2007 gab es mehr als 800 Mitglieder.

PCI Industrial Computer Manufacturers Group

Die 1994 gegründete PCI Industrial Computer Manufacturers Group (PICMG) ist ein Konsortium aus über 450 Firmen, die den PCI-Standard für die Nutzung im industriellen Bereich, in der Medizin, dem Militär und der Telekommunikation erweitern wollen. Daraus entstanden Spezifikationen wie CompactPCI oder AdvancedTCA.

Literatur

- Sonderheft PRAXIS PROFILINE Compact PCI PCI Express

- Don Anderson, Tom Shanley: PCI System Architecture 4th Edition. Mindshare Inc. 1999 ISBN 0-201-30974-2

Siehe auch

- PCI-Express

- Accelerated Graphics Port (AGP)

- Extended Industry Standard Architecture (EISA-Bus)

- VESA Local Bus (VLB)

- Industry Standard Architecture (ISA-Bus, auch AT-Bus genannt)

- Micro Channel Architecture (MCA-Bus)

- XT-Bus-Architektur

Weblinks

- ↑ Hardware and PCI Overview FAQs sun.com (4. Dezember 2008)

- PCI Special Interest Group (PCI-SIG) (englisch)

- PCI Local Bus Technical Summary (englisch)

- „Hardwerker“, Werkzeuge zur Fehlersuche - Enumeration PCI-Adapter durch BIOS und WinPnP

- Erklärung der Unterschiedlichen Steckplätze und Kombinationsmöglichkeiten der Karten

- PCI bus pinout

- PCI Technology Overview

- PCI-IDs bei Sourceforge.net

- Konventioneller PCI

Wikimedia Foundation.