- BEOL

-

Die Mikroelektronik ist ein Teilgebiet der Elektrotechnik bzw. der Elektronik, das sich mit der Miniaturisierung von elektronischen Schaltungen befasst.

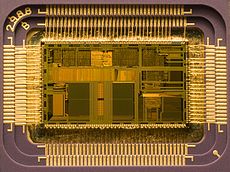

Integrierter Schaltkreis als Beispielanwendung aus dem Bereich Mikroelektronik. Das Chip-Gehäuse wurde geöffnet und ermöglicht den Blick auf den eigentlichen Halbleiter. Die erkennbaren Strukturen im Zentrum sind die realisierte elektronische Schaltung. Im Außenbereich sind die goldenen Anschlussleitungen zu erkennen, welche die elektrische Verdrahtung zwischen IC und den Gehäusekontakten bildet.

Integrierter Schaltkreis als Beispielanwendung aus dem Bereich Mikroelektronik. Das Chip-Gehäuse wurde geöffnet und ermöglicht den Blick auf den eigentlichen Halbleiter. Die erkennbaren Strukturen im Zentrum sind die realisierte elektronische Schaltung. Im Außenbereich sind die goldenen Anschlussleitungen zu erkennen, welche die elektrische Verdrahtung zwischen IC und den Gehäusekontakten bildet.Die Mikroelektronik hat zwei Hauptmerkmale:

- Integration (im Detail: siehe „Integrierte Schaltung“): Elektronische Schaltkreise werden auf einem gemeinsamen Substrat in einem gemeinsamen Fertigungsprozess erzeugt. Die Bausteine der Schaltungen bestehen zum größten Teil aus Transistoren, aber auch Widerständen, Kondensatoren und anderen Halbleiterbauelementen.

- Miniaturisierung: Die Bausteine der Schaltung (und damit die Schaltung als Ganzes) werden kontinuierlich verkleinert. Die Abmessungen eines Transistors liegen im Jahre 2004 deutlich unter einem Mikrometer. Damit lassen sich integrierte Schaltungen mit mehreren Millionen Transistoren auf einem Siliciumstück mit einer Kantenlänge von wenigen (typisch < 10) Millimetern realisieren.

Inhaltsverzeichnis

Anwendungen

Bauelemente der Mikroelektronik wurden ursprünglich für die Anforderungen der Raumfahrt nach kleinen und leichten Bauteilen entwickelt. Sie sind heute in einer Vielzahl technischer Geräte und Einrichtungen zu finden:

- In Computern sind essenzielle Bestandteile als mikroelektronische integrierte Schaltkreise ausgeführt: die zentrale Recheneinheit genauso wie der Arbeitsspeicher und eine Vielzahl unterstützender Controller und Schnittstellen-Bausteine.

- In der industriellen Fertigung finden sich mikroelektronische Bauteile auch zum Beispiel in den Maschinensteuerungen.

- In Geräten der Unterhaltungselektronik übernehmen integrierte Schaltungen neben der gesamten Steuerung der Geräte auch die Dekodierung komprimierter Filme beim DVD-Abspielgerät oder die Ansteuerung der einzelnen Bildpunkte eines Flachbildschirms.

- In allen Arten von Fahrzeugen wird die Mikroelektronik eingesetzt, unter anderem zur Motorsteuerung oder dazu, im richtigen Moment Sicherheitsfunktionen, wie Airbags, auszulösen. Für diesen Bereich müssen die mikroelektronischen Bausteine übrigens erhöhte Qualitätskriterien (z. B. den automotive temperature range) erfüllen.

- Moderne Kommunikationstechnik ist ebenfalls ohne Mikroelektronik nicht mehr denkbar, das gilt sowohl für die klassische Telefonie, als auch für die Datenkommunikation und den Mobilfunk.

An dieser Stelle kann nur eine exemplarische Auswahl genannt werden – es gibt sowohl in den genannten Gebieten eine Vielzahl weiterer Anwendungen als auch eine Reihe hier nicht genannter Anwendungsgebiete, wie Medizintechnik, Gebäudetechnik und vieles mehr.

Bauelemente

Die mikroelektronischen Bauelemente lassen sich zunächst in zwei große Gruppen einteilen: Standardbausteine und Anwendungsspezifische:

- Standard-ICs lassen sich in einer Vielzahl von Anwendungen einsetzen, werden in großer Zahl produziert und sind teilweise auch tatsächlich durch Standardisierungskonsortien in ihrer Ausprägung festgelegt (Abgrenzung in der Praxis unscharf)

- Mikroprozessor (MPU – Micro Processor Unit) – Schaltkreise, die keine eindeutig definierte Eingangs-Ausgangsrelation haben, sondern eine Abfolge von Operationsanweisungen – ein Programm – abarbeiten

- Mikrocontroller (MCU – Micro Controller Unit) – Ein-Chip-Computersystem, das einen Mikroprozessor, verschiedene Schnittstellen (Peripherals) und Speicher (RAM und ROM) enthält.

- Digitale Signalprozessoren (DSP – Digital Signal Processor) – ähnlich einem Mikrocontroller, aber spezialisiert auf Signalverarbeitung (digitale Repräsentierungen analoger Daten, z. B. Musik)

- Dynamische Speicherbausteine – preiswerte Speicherform, die vorwiegend als Arbeitsspeicher Verwendung findet

- Flash-EEPROMs – nichtflüchtiger Speicher, der nur blockweise geschrieben werden kann, häufig in Form von Speicherkarten zur Speicherung digitaler Musik, etc. eingesetzt

- Andere Speicherbausteine: SRAM, ROM, PROM, EPROM, ...

- Programmierbare Logikbausteine (PLD – programmable logic devices) – integrierte Schaltkreise, die nach Fertigstellung noch für beliebige spezifische Logikfunktionen konfiguriert werden können. Einen Sonderfall stellen die FPGAs (field programmable gate array) dar, deren Funktionalität praktisch beliebig oft geändert werden kann. Dafür werden auf diesen Chips nichtflüchtige Speicher oder externe Konfigurationsspeicher benutzt.

- Anwendungsspezifische ICs: Schaltkreise, die für eine bestimmte Anwendung (z. B. Motorsteuerung im Auto) entworfen und gebaut sind und von ihrem Funktionsumfang keine andere Anwendung erlauben.

- Applikationsspezifische Standardprodukte (ASSP – application specific standard product) – ein Logikschaltkreis, dessen Funktion fest definiert ist, der jedoch von mehreren Kunden genutzt werden kann (z. B. Applikationsprozessor für Handys)

- Anwendungsspezifische Integrierte Schaltung (ASIC – application specific integrated circuit) - ein Logikschaltkreis, dessen Funktion ebenfalls fest definiert ist, der aber speziell für einen Kunden bzw. eine Anwendung entworfen und gebaut wird (in der Praxis werden mit diesem Begriff häufig auch alle festdefinierten Logikbausteine assoziiert – ASIC und ASSP)

Neben dieser Systematik wird eine Gruppe von Bauelementen meist extra aufgeführt:

- Analoge ICs: integrierte Schaltungen, die analoge Signale, wie Spannungen oder Ströme, direkt – d. h. ohne Umwandlung in digitale Signale – verarbeiten.

Fertigung von integrierten Schaltkreisen

Man unterscheidet die Festkörpertechnik (auch: monolithische Fertigung) von den Filmtechniken.

- Die Dünnfilmtechnik und Dickfilmtechnik, bei denen Bauteile auf einen Film aufgebracht oder eingebettet und verbunden werden, haben nur noch für Spezialanwendungen (Hochfrequenztechnik) Bedeutung. Als Hybridtechnik bezeichnet man die Kombination der Filmtechnik und Festkörpertechnik. Dabei werden in Festkörpertechnik hergestellte Halbleiterchips auf einem Trägermaterial aufgebracht und dann in Filmtechnik darauf z. B. Verbindungsleitungen und passive Bauelemente realisiert.

- Bei der Festkörpertechnik können diese grundlegenden Fertigungsabschnitte unterschieden werden:

Rohwaferherstellung

Das Grundmaterial (Substrat) der überwiegenden Mehrzahl (mehr als 99 %) der integrierten Schaltkreise ist einkristallines Silicium, das gleichzeitig als aktives Material für die Transistoren dient. Für sehr hochfrequente oder optische Anwendungen kommen auch andere Materialien wie Gallium-Arsenid zum Einsatz. Für spezielle Anwendungen wird auch Silicium auf dem isolierenden Substrat Saphir verwendet (SOS für Silicon on Saphire).

Zunächst wird aus einer hochreinen Siliciumschmelze ein einkristalliner Zylinder (Ingot) gezogen und durch Zonenschmelzen weiter gereinigt. Dieser wird in 0,5–1,5 mm dünne Scheiben, die sog. Wafer, zersägt. Die heute in der Massenproduktion verwendeten Siliciumwafer haben Durchmesser von 6, 8 oder 12 Zoll (entsprechend 150, 200 oder 300 mm). Sie erhalten durch verschiedene Ätz-, Schleif- und Polierprozesse eine nahezu perfekte ebene Oberfläche mit Unebenheiten in der Größenordnung von wenigen nm. Die Dickenschwankungen (TTV-Werte, Total Thickness Variation) liegen im Bereich von wenigen Mikrometern.

Front-End-Fertigung

Auf einem Wafer werden hunderte und bei einfachen Strukturen (z. B. Einzeltransistoren) hunderttausende identische integrierte Schaltkreise (engl. IC oder chip) parallel hergestellt.

Die Fertigung erfolgt in extrem sauberer Umgebung, so genannten Reinräumen, mit einer sehr geringen Dichte von Staubpartikeln. Dies ist nötig, weil selbst kleinste Partikel (< 0,1 µm) bereits den Ausfall eines kompletten Schaltkreises verursachen können.

Der Herstellungsprozess umfasst chemische und physikalische Prozessschritte des Wafers und muss stetig an die neuesten Minaturisierungsanforderungen angepasst werden. Für jeden Prozessschritt müssen durch Fotolithografie die Bereiche auf dem Wafer festgelegt werden, die im nachfolgenden Prozessschritt die jeweilige chemische oder physikalische Bearbeitung erhalten sollen. Hieraus entwickelte sich eine eigene Halbleitertechnologie, die sich sowohl mit den Anforderungen einer Einzelstruktur auseinandersetzt, als auch das Zusammenspiel aller Einzelstrukturen zu einer funktionsfähigen elektrischen Schaltung sicherstellen muss. Hochintegrierte Schaltungen wie Prozessoren oder Mikrocontroller durchlaufen dazu über 30 Strukturierungsdurchläufe.

Üblicherweise wird der gesamte Fertigungsdurchlauf in zwei Bereiche unterteilt:

- das „front-end of line“ (FEOL, dt. »vorderes Ende der Produktionslinie«) bezeichnet die Strukturierungsebenen, in denen die Funktionsblöcke erzeugt werden;

- das „back-end of line“ (BEOL, dt. »hinteres Ende der Produktionslinie«) (nicht zu verwechseln mit Back-End-Fertigung) umfasst die Verdrahtung und abschließende Passivierung der Oberfläche. Zur Verdrahtung bzw. Metallisierung wird Aluminium oder Kupfer benutzt. Insbesondere die Bearbeitung mittels Kupfer wird räumlich von der FEOL getrennt, um eine Kontamination der FEOL auszuschließen.

Bei einigen Front-End-Technologien, wie beispielsweise IGBT, werden zusätzlich die der Schaltung entgegengesetzte Seite metallisiert, um einen leitenden Kontakt herzustellen.

Den Abschluss bildet der PCM-Test (process control monitoring, dt. Prozessüberwachung). Damit werden Teststrukturen gemessen, die sich i. A. zwischen den ICs im sogenannten „Ritzrahmen“ befinden. Diese Teststrukturen lassen Rückschlüsse über die Qualität der Einzel- bzw. des Gesamtprozesses zu.

Funktionstest

Die ICs müssen vor der Weiterverarbeitung auf ihre Funktion getestet werden. Teilweise sind bestimmte Funktionen (HF-Schaltungen oder später nicht auf PINs herausgeführte Anschlüsse des Chips) nur auf dem Die testbar. Vor allem muss aus Kostengründen verhindert werden, dass nicht funktionsfähige ICs im nachfolgenden Herstellungsprozess weiterbearbeitet werden. Dabei werden die wichtigsten elektrischen Parameter der verwendeten Bauelemente an speziellen Teststrukturen ermittelt. Diese müssen bestimmte Spezifikationen einhalten, um sicherzustellen, dass die Chips im gesamten zulässigen Temperaturbereich und über die volle spezifizierte Lebensdauer zuverlässig arbeiten.

Obwohl diese Messungen auf speziellen Testsystemen (Automatic Test Equipment) vollautomatisch ablaufen, haben die damit verbundenen Kosten bei hochintegrierten Prozessorchips bereits nahezu die Herstellungskosten erreicht. Dies liegt vor allem daran, dass nur bedingt Skaleneffekte beim Testen greifen (eine Parallelisierung ist beispielsweise nur bei reinen Digitalschaltungen möglich) und neuere ICs immer mehr Funktionen beinhalten, die nacheinander getestet werden müssen.

Bei allen neuen FE-Technologien wird eine Lernkurve durchlaufen, die sich u. a. an der Ausbeute funktionierender Bausteine messen lässt (Yield). Da eine neue FE Technologie erhebliche Entwicklungskosten (z. T. 3-stellige Millionenbeträge) beinhaltet, haben die Firmen ökonomische Vorteile, die möglichst schnell hohe Yield Werte erzielen.

Back-End-Fertigung

Zur Verwendung auf einer Leiterplatte muss der empfindliche Chip in ein Gehäuse eingebaut werden. Dazu werden die kompletten Wafer auf die richtige Dicke geschliffen („backlapping“), dann in die einzelnen Dies zersägt (vereinzelt). Da die Säge ein Stück aus dem Wafer entfernt, sind die Chips nicht nahtlos nebeneinander angeordnet, sondern haben einen gewissen Abstand. In diesen Bahnen (dem sog. „Ritzrahmen“) sind zudem Teststrukturen aufgebracht die zur PCM Messung unmittelbar nach der Front-End-Fertigung genutzt werden. Diese Teststrukturen werden beim Sägen zerstört. Damit beim Sägen die einzelnen Dies nicht auseinanderfallen, wird vor dem Sägen der Wafer auf eine Sägefolie aus Kunststoff aufgeklebt.

Chips in oberflächenmontierten Plastikgehäusen auf einer Computer-Platine (Makroaufnahme)

Chips in oberflächenmontierten Plastikgehäusen auf einer Computer-Platine (Makroaufnahme)Der Chip wird nach dem Sägen in das Gehäuse eingesetzt. Dazu wird der Chip von der Sägefolie aufgenommen und auf das Leadframe geklebt (Chipbonden). Schließlich werden die Anschlüsse auf dem Chip mit dünnen Golddrähten mit den Anschlüssen (Pins) des Gehäuses verbunden (Drahtbonden). Der Chip wird dann in ein Gehäuse eingebaut, meistens mit Spritzgusstechnik in ein Kunststoffgehäuse, seltener auch in ein - teures - Keramikgehäuse (dies insbesondere bei Prototypen und Kleinserien, oder wenn ein Kunststoffgehäuse nicht geeignet wäre). Als letzter Schritt wird das Gehäuse mit Informationen des Herstellers bedruckt, z. B. mit dem Herstellernamen, der Typennummer, dem Herstellungsdatum u.ä.). Die Back-End-Fertigung wird im Gegensatz zur Front-End-Fertigung von Mikromechanik und Verfahren der Kunststoffbearbeitung (Spritzguss) dominiert.

Endprüfung

Schließlich wird auch der gehäuste Chip vor der Ablieferung einem endgültigen Test unterzogen, um Fehler in der Back-End-Fertigung festzustellen. Auch werden einige Eigenschaften getestet, die sich durch das Packaging verändern bzw. deren Messung ohne Gehäuse nicht möglich ist, wie z. B. das Bonding oder bestimmte Hochfrequenzeigenschaften. Der gehäuste Chip kann dann zur Leiterplattenbestückung gehen.

Prüfen von Mikrostrukturen

Um die feinen Strukturen der Mikroelektronik auflösen zu können, werden heutzutage Starrnadeladapter eingesetzt, mit welchen ein Messpunktabstand von 150 µm aufgelöst werden können. Durch das präzise Führen der Starrnadeln können mit solchen Adaptern Kontaktstellen mit einem Durchmesser von 70 µm abgegriffen und geprüft werden. Als weiteres ermöglicht der Starrnadeladapter auch das Kontaktieren von feinpoligen Mikrosteckern, welche heutzutage in der Mikroelektronik immer mehr ihre Anwendung finden. Somit müssen solche Stecker nicht mehr mit dem schnell verschlissenen Gegenstecker kontaktiert werden.

Entwicklung mikroelektronischer Bauelemente

Beim Chipentwurf geht es darum, die Grundelemente der mikroelektronischen Schaltungen – Dioden, Transistoren, passive Bauteile, Leiterbahnen – zu der gewünschten Funktion zu verknüpfen, geometrisch auf der Siliciumfläche anzuordnen und physikalisch ihr Verhalten zu modellieren. Die spezifischen Charakteristika der Mikroelektronik haben dazu geführt, dass sich ein spezieller Entwurfsprozess ausgebildet hat.

Der Produktion eines Chips gehen sehr hohe Einmalkosten (NRE – engl. non recurring engineering costs) voraus (z. B. Maskenkosten, siehe Fotolithografie). Auch ist eine Reparatur eines integrierten Schaltkreises nur sehr eingeschränkt möglich und produktiv nicht praktikabel. Daher ist es von großer Bedeutung, dass der Entwurf nur mit wenigen Überarbeitungen (sog. Redesigns) zum gewünschten Produkt führt. Das hat zur Folge, dass zu einem erheblichen Anteil Simulations- und Verifikationsschritte den Entwicklungsverlauf bestimmen – im Jahre 2004 machen sie etwa die Hälfte des Entwicklungsaufwandes für den Schaltkreis aus – mit steigender Tendenz.

Die Verkleinerung und steigende Integration führen zu einer immensen Anzahl von realisierbaren Funktionselementen (= meist Transistoren; mehrere Millionen im Jahre 2004) in einer integrierten Schaltung. In diesem Umfang können die Transistoren nicht mehr mit vertretbarem Aufwand „von Hand“ in eine Schaltung umgesetzt werden. Daher gewinnt die Entwurfsautomatisierung immer weiter an Bedeutung. In vielen Fällen beschreibt der Chipentwickler die gewünschte Schaltung bei digitalen Schaltungsblöcken nur noch in einer „Hochsprache“ (vergleichbar der höheren Programmiersprache in der Informatik, übliche Ausprägungen: VHDL, Verilog), der Computer errechnet daraus die Schaltnetze (Synthese, engl. synthesis) und platziert die Transistoren (unter menschlicher Mitwirkung und Kontrolle). Für analoge Schaltungen werden die entworfenen Schaltungen in sehr vielen Simulationsläufen (mit SPICE o. ä.) charakterisiert, wobei viele verschiedene Kombinationen für Betriebstemperaturen und -spannungen, Prozessvariationen u. ä. simuliert werden. Häufig werden auch statistische Variationen mit Hilfe einer Monte-Carlo-Analyse simuliert. Für Digital- wie für Analogschaltungen kann das Layout extrahiert werden um parasitäre Elemente in der Simulation zu berücksichtigen und somit realistischere Ergebnisse zu erreichen.

Die fortschreitende Miniaturisierung treibt sowohl die Strukturierungsprozesse als auch die realisierten Funktionsbausteine, wie Transistoren und Leiterbahnen, an ihre physikalischen Grenzen. Um Ersterem zu begegnen, wird im Entwurfsprozess in steigendem Umfang Software eingesetzt, die die physikalischen Grenzeffekte, wie z. B. die optische Beugung bei der Fotolithografie simuliert und den Schaltungsentwurf so modifiziert, dass diese Effekte ausgeglichen werden (sog. OPC, engl. optical proximity correction). Um den Miniaturisierungseffekten bei den Bauelementen entgegenzuwirken, kommen fortlaufend neue Simulations- und Modellierungsverfahren zum Chipentwurfsprozess hinzu: zum Beispiel Simulationen des Spannungsabfalls in langen Versorgungsnetzen (IR drop), Simulation der parasitären kapazitativen Kopplung benachbarter Leiterbahnen, Werkzeuge zur statischen Analyse der Zeitverhältnisse in einer Digitalschaltung (sog. STA, engl. static timing analysis ) usf.

Um Prototypen eines neuen Chips einigermaßen kostengünstig zu fertigen, kann man die Layouts mehrerer Chips auf einem Wafer zusammenfügen (sog. MPW - Multi-Projekt-Wafer), da sich so die Masken- und Fertigungskosten für die vergleichsweise kleinen Prototypenstückzahlen auf mehrere Projekte verteilen lassen.

Gründe und Folgen der Miniaturisierung

Seit Gordon Moore 1965 das nach ihm benannte 'Gesetz' formulierte, dass sich die Anzahl der Transistoren auf einem Chip alle zwölf Monate (später achtzehn Monate) verdopple, hat die Mikroelektronik tatsächlich sowohl in Hinblick auf Integrationsdichte als auch bei der Verkleinerung der Strukturen kontinuierliche Fortschritte gemacht.

Der Treiber für die Verkleinerung der Strukturen ist die Senkung der Fertigungskosten. Die Fertigung von Mikrochips erfolgt auf Halbleiterscheiben (Wafer) konstanter Größe (tatsächlich gibt es eine Evolution der Scheibengröße über die Zeit, aber die ist für diese Betrachtung hinreichend langsam). Daher lassen sich die Fertigungskosten zunächst als Summe der Prozesskosten pro Wafer beschreiben (mit einer gewissen Abstraktion und unter Vernachlässigung der Kosten für Tests und Gehäuse der ICs). Insofern gibt es auf die Fertigungskosten pro Chip zwei Hebel:

- Anzahl der Chips pro Wafer

- Summe der Kosten für die strukturierenden und eigenschaftsändernden Prozesse pro Wafer

Ersteres nimmt durch die Minimierung der Strukturbreite überproportional zu (Flächenreduktion ist gleich Längenmaßreduktion zum Quadrat plus bessere Randausnutzung minus nichtlineare Effekte).

Zweitens (die Prozesskosten der Strukturierungsprozesse und die Anzahl notwendiger Prozessschritte) nehmen jedoch mit steigender Miniaturisierung meist ebenfalls zu. Bis heute (2004) hat die Halbleiterindustrie damit eine durchschnittliche Fertigungskostenreduktion von 30 % pro Jahr erreicht. Ein mögliches Szenario kann sein, dass die Zunahme der Prozesskosten bei Annäherung an physikalische Grenzen nicht mehr hinreichend durch die Einsparung der Chipfläche kompensiert werden kann und der Fortschritt in der Miniaturisierung sich dadurch verlangsamt bzw. endet. Außerdem lassen sich einige Sonderschaltungstechniken (z. B. solche zur Erzielung höherer Spannungen als die Versorgungsspannung(en) des Chips) heute (2006) schon nicht mehr herunterskalieren.

Die hohe konstante Fertigungskostenreduktion in der Mikroelektronik war ein wesentlicher Innovationsmotor der letzten dreißig Jahre in einer Vielzahl von Branchen - nicht allein in der Elektronik und Computertechnik (siehe Anwendungen).

Neben der Kostensenkung gibt es aber auch andere Effekte der Miniaturisierung:

- Kleinere Schaltelemente, die bei verringerter Spannung betrieben werden, haben auch eine wesentlich verringerte Verlustleistung (die Verlustleistung pro Fläche steigt jedoch → schlechtere Wärmeabfuhr). Ohne Verkleinerung und Integration wäre batteriebetriebene, mobile Elektronik nicht denkbar, wie sie heute allgegenwärtig ist: Mobiltelefon, Notebook, PDA etc.

- Kleinere Transistoren haben verbesserte Schaltzeiten, kürzere Leiterbahnen verkürzte Signallaufzeiten: durch die Verkleinerung werden immer schnellere und damit meist auch leistungsfähigere Schaltungen möglich. Allerdings gibt es auch gegenläufige Effekte: Die verkürzten Abstände zwischen den Leiterbahnen führen zu höheren Koppelkapazitäten, die als Laufzeitbremse wirken.

- Höhere Integration (mehr Funktionen auf einem Chip) bedeutet weniger Bauelemente auf einer Leiterplatte und damit erhöhte Zuverlässigkeit durch weniger Lötverbindungen.

Ökonomie

Der Industriezweig, der sich mit der Herstellung von mikroelektronischen Bauteilen beschäftigt – die Halbleiterindustrie – zeigt zwei Eigenschaften, die ihn von anderen unterscheidet.

Große Skaleneffekte: Halbleiterfabriken für die Massenfertigung von Bausteinen der jeweils kleinstmöglichen Strukturgrößen sind erst ab einer gewissen Größe rentabel. Weiterhin sind diese Fabriken um Größenordnungen teurer als vergleichbare Fertigungsstätten anderer Branchen: heute (2004) liegen die Kosten für Bau und Ausrüstung einer Hochvolumenfabrik auf dem Stand der Technik bei etwa US$ 2 Milliarden. Beides zusammen führt zu dem so genannten Schweinezyklus: Es gibt nur eine vergleichsweise geringe Anzahl an aktuellen Halbleiterfabriken weltweit. Wenn es der Branche gut geht, d. h. in der Regel, wenn das Angebot an Halbleiterbausteinen geringer ist als die Nachfrage, baut sie ihre Fertigungskapazitäten aus, weil die meisten Unternehmen nur dann die Summen für den Ausbau aufbringen können. Jede neue Fabrik, die in Produktion geht, erhöht das Weltmarktvolumen verfügbarer Bausteine gleich um Prozentpunkte, da sie ja aus Rentabilitätsgründen sehr groß sein müssen. Der schlagartige Anstieg verfügbaren Volumens führt zu einem entsprechend starken Preisverfall der Bauelemente, der sich wieder einschwingt, sobald die Nachfrage das Angebot wieder eingeholt hat. Durch den Preisverfall sind viele Unternehmen eine Zeit lang nicht in der Lage ihre Fertigungskapazitäten auszubauen – es läuft auf die nächste Verknappung des Angebotes zu. Dann wiederholt sich der Zyklus.

Zuschreibung strategischer Bedeutung: Viele Staaten schreiben der Halbleiterindustrie strategische Bedeutung zu. Meist begründet sich das in dem „Keimzelleneffekt“ für andere Hochtechnologien: Im Umfeld von Halbleiterindustrien entwickeln sich nicht nur hochqualifizierte Zulieferer aus der Chemie und dem Anlagenbau, sondern auch aus den Abnehmerindustrien der Bauelemente, zum Beispiel die Computer- und Elektronikindustrie. In einigen Fällen wird die strategische Bedeutung auch militärisch begründet: So schätzen die USA die Bedeutung der Mikroelektronik für Rüstungsprogramme so wichtig ein, dass sowohl Geräte zur Herstellung aktueller ICs als auch die Schaltungsentwürfe und sogar die Schaltungsentwicklungssoftware Gegenstand ihrer Exportkontrolllisten sind. Diese hoch eingeschätzte Bedeutung hat zur Folge, dass eine Vielzahl von Staaten die Ansiedelung der Halbleiterindustrie in vielerlei Weise fördern: von Anschubfinanzierungen, besonderen Steuergestaltungen, staatlichen Kreditgarantien bis zu staatlich geförderter Forschung an universitären und industriellen Forschungszentren, etc. Diese Förderungen sind auch gelegentlich Gegenstand von ökonomischen Auseinandersetzungen zwischen Staaten und Unternehmen – so geschehen zuletzt im Jahre 2003: nachdem dem DRAM-Hersteller Hynix vorgeworfen wurde über die Maßen vom südkoreanischen Staat in seiner Finanzkrise gestützt worden zu sein, erwirkten die USA, die Europäische Union und zuletzt Japan Strafzölle auf die Produkte dieses Unternehmens, wogegen Südkorea protestierte.

Geschäftsmodelle: Wie in vielen anderen Branchen auch gibt es den Vollhersteller – Integrated Device Manufacturer (IDM) genannt. Ein IDM erstellt das Produktdesign, entwickelt die Fertigungstechnologie, fertigt das Bauteil und verkauft es selbst. Daneben gibt es jedoch auch noch die „Fabless Design Houses“ und „Foundries“. Fabless Design Houses erstellen das Produktdesign entsprechend den Vorgaben der Foundry, die es später fertigen wird und verkaufen das fertige Produkt. Die Foundry entwickelt die Fertigungstechnologie, stellt ihren Kunden technologiespezifische Hilfsmittel zum Chipentwurf (EDA) bereit und fertigt die ICs. Kombinationen dieser Geschäftsmodelle und Nischenmodelle sind in der Praxis auch zu finden.

Geschichte

- 1904 Die erste Elektronenröhre, eine Röhrendiode wird von John Ambrose Fleming entwickelt.

- 1906 Von Lee de Forest wird Flemings Röhrendiode modifiziert. Er ergänzte diese um eine dritte Elektrode und schuf damit die Triodenröhre, den Vorläufer des Transistors.

- 1946 In den USA wird der Großrechner ENIAC in Betrieb genommen. Er arbeitet mit 14468 Elektronenröhren.

- 1947 John Bardeen, Walter Brattain und William B. Shockley entdecken den Transistoreffekt und stellen

- 1948 den ersten Transistor aus Germanium vor.

- 1954 Der erste Transistor aus Silicium wird vorgestellt. William Shockley eröffnet ein Labor nah der Stanford Universität in Palo Alto, die als Keimzelle von Silicon Valley gilt. In diesem Jahr beginnt auch der Wettstreit um den besseren Halbleiter-Grundstoff: Germanium oder Silicium.

- 1956 William Shockley erhält einen Nobelpreis für seine Arbeiten. Shockley hält Germanium für den besseren Grundstoff, seine Schüler Silicium.

- 1957 Shockleys Schüler trennen sich von ihrem Lehrer. Sie werden als „acht Verräter“ bezeichnet: Eugene Klinger, Jay Last, Victor Ginrich, Jean Hoerni, Sheldon Roberts, Julius Blank, Gordon E. Moore, Robert N. Noyce. Die „acht Verräter“ bilden mit einem Wagniskapital die Fairchild Semiconductor Corporation.

- 1958: Fairchild Semiconductor stellt den ersten Transistor basierend aus dem Grundstoff Silicium in Serienstückzahlen zur Verfügung.

- 1959: Jack Kilby, Angestellter bei Texas Instruments zieht Konsequenz aus der Tatsache, dass Transistoren wie Widerstände aus einem einzigen Material gefertigt werden. Er bringt erstmals eine Schaltung aus verschiedenen Komponenten auf einem einzigen Substrat unter. Damit ist der Integrierte Schaltkreis (IC) erfunden. Im September führt er dann den Chip, auf Basis eines Germanium-Substrates, vor. Aus dieser Arbeit heraus entsteht das berühmte Kilby-Patent (japanisches Patent Anmeldungs-Nr. 320.275, vom japanischen Patentamt und durch das Obergericht (OG) Tokyo wegen fehlender erfinderischer Tätigkeit zurückgewiesen[1]). Um dieses Patent wurde rund zehn Jahre vor Gericht gestritten, da Robert N. Noyce einen sehr ähnlichen Schritt erdacht hatte, diesen allerdings später zum Patent anmeldet.[2]

- 1960: Jean Hoerni (Fairchild Semiconductor) erfindet das Planar-Verfahren und revolutioniert damit die Halbleiterherstellung.

- 1961: Erste integrierte Schaltkreise mit wenigen Bipolartransistoren und Widerständen werden realisiert.

- 1968: Robert N. Noyce verlässt Fairchild Semiconductor, um zusammen mit Gordon Moore die Firma Intel in Santa Clara zu gründen.

- ab 1970: Es werden höhere Transistordichten mit einigen tausend Bauelementen realisiert. Dies wird als Großintegration (LSI Large Scale Integration) bezeichnet. Die bipolaren Transistoren werden durch Feldeffekttransistoren FETs, meist in der Form von leicht herstellbaren MOSFETS (Metal Oxide Semiconductor Field Effect Transistor) ersetzt.

- 1979: Es beginnt die Größtintegration (VLSI Very Large Scale Integration) mit heute mehreren Millionen Transistorfunktionen und früher unerreichbaren Taktfrequenzen von mehreren Gigahertz. Die Größe des Einzelbauteils liegt dabei weit unter einem Quadratmikrometer. Zunehmend werden auch ganze Systeme (Kombination mehrerer Baugruppen, wie Prozessoren, Schnittstellenschaltungen und Speichern) auf einem einzelnen Chip realisiert (SoC System on a Chip).

Zukünftige Entwicklungen

Unterschreiten Strukturgrößen die 100-Nanometer-Grenze (2008 sind sie bereits bei 45 nm bzw. 2009 bei 40 nm), so spricht man formal bereits von Nanoelektronik bzw. Nanotechnologie (Definition der US-Regierung). Im engeren Sinne ist jedoch eher gemeint, dass besondere Materialeigenschaften genutzt werden, die erst auftreten, wenn sich die Strukturabmessungen in der Nähe der Molekül- bzw. der Atomgröße bewegen. Zu solchen Strukturen zählen zum Beispiel Leitungsbahnen oder Transistoren aus Kohlenstoffnanoröhren oder Isolationen aus Self Assembling Monolayern.

Neue Bauelemente werden mit Resonanztunneldioden aufgebaut.

Integrierte Optoelektronik: Angesichts zunehmender Signallaufzeiten insbesondere in langen Verbindungsleitungen (globale Interconnects) großer System on a Chips wird darüber nachgedacht, diese elektrischen Leitungen durch optische Verbindungen zu ersetzen.

Organische Elektronik: um kostengünstige „Wegwerfelektronik“ (z. B. elektronische Preisetiketten) zu realisieren, werden Schaltungen auf der Basis organischer und metallischer Materialien auf organischen Substraten in Dünnschichttechnik aufgebracht (siehe Organischer Feldeffekttransistor).

Einzelnachweise

- ↑ Klaus Hinkelmann: Berücksichtigung der Rechtsbeständigkeit von Patenten in Patentverletzungsverfahren: Übersetzung und Kommentierung der Entscheidung des Obersten Gerichtshofes vom 11. April 2000. In: Zeitschrift für Japanisches Recht. Nr. 10, 2000, S. 266–273 ([1]).

- ↑ Robert N. Noyce: Semiconductor device and lead structure. US-Patent 2.981.877, angemeldet am 30. Juli 1959, angenommen am 25. April 1961. ([2])

Literatur

- Simon M. Sze: Physics of Semiconductor Devices. 2. Auflage. John Wiley and Sons, 1981, ISBN 0-471-05661-8

- Ulrich Hilleringmann: Silizium-Halbleitertechnologie. Teubner, 2004, ISBN 3-519-30149-0

- Ulrich Tietze, Christoph Schenk, Eberhard Gamm: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6

- Michael Reisch: Halbleiter-Bauelemente. Springer, 2004, ISBN 3-540-21384-8

- Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer: Analysis And Design Of Analog Integrated Circuits. 4. Auflage. John Wiley and Sons, 2001, ISBN 0-471-32168-0

Siehe auch

Wikimedia Foundation.