- Sperrschicht-Feldeffekttransistor

-

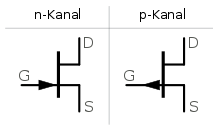

Der Sperrschicht-Feldeffekttransistor (SFET, engl. junction-fet, JFET bzw. non-insulated-gate-fet, NIGFET) ist der am einfachsten aufgebaute Unipolartransistor aus der Gruppe der Feldeffekttransistoren; man unterscheidet zwischen n-Kanal- und p-Kanal-JFETs.

Schaltsymbole von JFETs

Schaltsymbole von JFETs

Inhaltsverzeichnis

Geschichte

Die Entwicklung des Sperrschicht-Feldeffekttransistors geht auf Julius Edgar Lilienfeld zurück, welcher 1925 die Funktionsweise erstmals beschrieb. Allerdings war damals fertigungstechnisch die Dotierung des Halbleitermaterials noch nicht soweit fortgeschritten, um JFETs reproduzierbar herstellen zu können.[1] Die ersten praktisch realisierten JFET mit einem p-n-Übergang (positiv-negativ) und einem sogenannten Gate als Steuerelektrode gehen auf Herbert F. Mataré, Heinrich Welker und parallel dazu William B. Shockley und Walter H. Brattain aus dem Jahr 1945 zurück.[2]

Aufbau

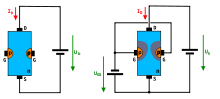

Die folgenden Erläuterungen beziehen sich auf n-Kanal-JFETs. Beim p-Kanal-JFET sind die n- und p-Zonen vertauscht und die Vorzeichen aller Spannungen und Ströme kehren sich um.

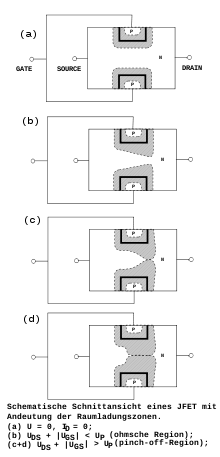

Ein n-Kanal-JFET besteht aus einem n-dotierten Bereich, welcher von einer p-Zone (Sperrschicht) umschlossen wird (siehe auch p-n-Übergang). An der n-Schicht sind die Anschlüsse Drain (D; Drain = Senke, Abfluss) und Source (S; Source = Quelle, Zufluss) einlegiert. Die Drain-Source-Strecke nennt man n-Kanal.

Die p-Zone ist der so genannte Gate-Anschluss (G; Gate = Tor). Dieser Anschluss dient der Steuerung des JFETs. Er bildet mit dem n-Kanal eine p-n-Diode. Der JFET ähnelt somit dem MESFET (engl. metal-semiconductor FET) bei dem anstelle des p-n-Übergangs ein Metall-Halbleiter-Übergang (Schottky-Übergang) verwendet wird. In der Funktionsweise unterscheiden sich JFET und MESFET nicht.

Funktion

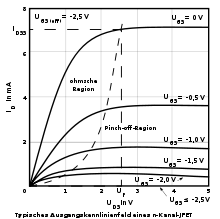

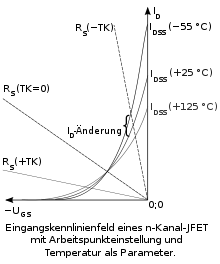

Bei offenem Gate-Anschluss verhält sich der n-Kanal ähnlich wie ein ohmscher Widerstand. Ohne Ansteuerung am Gate ist der JFET also leitend. Wird das Gate mit der Source verbunden und zusätzlich die Drain-Source-Spannung UDS am n-Kanal erhöht, so steigt der Strom solange an, bis eine maximale Einschnürung des Kanals erreicht wurde. Diese Spannung wird als Abschnür- oder pinch-off-Spannung Up (siehe Ausgangskennlinie) bezeichnet, sie entspricht der Schwellspannung Uth bei MOSFETs. Bei weiterer Erhöhung von UDS bleibt der Drainstrom ID nahezu konstant. Die Einschnürung hat sich stabilisiert und horizontal (im Beispielbild) ausgedehnt, d. h., die „zusätzliche“ Kanalspannung wird nun vom „pinch off“ weg, im Kanal absorbiert. Dies ist der normale Arbeitsbereich dieses Transistors und der entsprechende Drainstrom wird IDSS (von engl. drain sourceshorted to gate) genannt. Der Transistor kann in diesem Zustand (quasi) als Konstantstromquelle mit IDSS verwendet werden, nachteilig gegenüber „richtigen“ Konstantstromquellen ist eine erhöhte Temperaturabhängigkeit. Die Größe der pinch-off-Spannung ist abhängig von der Dotierung ND bzw. A und der halben Breite a des Kanals, sowie von dem Spannungsabfall UD (Diffusionsspannung) über die Raumladungszonen:

- Up = UD − Up0

mit der inneren pinch-off-Spannung:

Hierbei ist e die Elementarladung. Die pinch-off-Spannung wird im Falle eines n-Kanals in Gate-Source-Richtung und in Falle eines p-Kanals in Source-Gate-Richtung positiv gezählt.

Durch Anlegen einer negativen Vorspannung zwischen Gate und Source wird die Raumladungszone der Gate-Source-Diode vergrößert (n-Kanal-JFET). Der Kanal wird in der Breite und Länge zusätzlich moduliert (Pinch-Off-Region; siehe Bild).[3][4][5] Dadurch ist eine Steuerwirkung bei hohem Ausgangswiderstand am Drain möglich (ähnlich wie beim Bipolartransistor oder einer Pentode). Im Ausgangskennlinienfeld ist zu sehen, dass sich der Strom der horizontalen Kennlinienäste im aktiven Bereich zu kleineren Werten verschiebt. Auch in diesem Fall bewirkt eine Erhöhung der Drain-Source-Spannung nur eine sehr geringe Änderung des Drainstroms.

Die gewünschte Arbeitspunkteinstellung für den Betrieb ist sehr einfach und geschieht, analog zu einer Elektronenröhre, entweder mit einem Source-Widerstand oder durch eine negative Gate-Source-Vorspannung. Wie bei einer Elektronenröhre ist auch beim JFET die Steilheit

sehr gering und für eine hohe Spannungsverstärkung sind z. B. relativ große Arbeitswiderstände erforderlich. Vorteilhaft ist, wie bei der Elektronenröhre oder MOSFETs, die nahezu leistungslose Steuerung des JFETs (für den stationären Betrieb). Da die zum Steuern des Drainstromes verwendete Gate-Source-Strecke immer in Sperrrichtung betrieben wird, fließt durch das Gate nie mehr als der Sperrstrom von einigen Picoampere. Bei höheren Frequenzen treten kapazitive Ströme auf.

sehr gering und für eine hohe Spannungsverstärkung sind z. B. relativ große Arbeitswiderstände erforderlich. Vorteilhaft ist, wie bei der Elektronenröhre oder MOSFETs, die nahezu leistungslose Steuerung des JFETs (für den stationären Betrieb). Da die zum Steuern des Drainstromes verwendete Gate-Source-Strecke immer in Sperrrichtung betrieben wird, fließt durch das Gate nie mehr als der Sperrstrom von einigen Picoampere. Bei höheren Frequenzen treten kapazitive Ströme auf.Wird der JFET unterhalb der Pinch-Off-Spannung im linearen Bereich betrieben (ohmsche Region; siehe Bild), kann er z. B. für eine automatische Verstärkungsregelung (engl. automatic gain control, AGC) als Teil eines Spannungsteilers verwendet werden. Er verhält sich dort ähnlich einer Triode.

Die Steuerkennlinie (ID als Funktion von UGS) ist eine komplizierte Funktion und kann durch eine quadratische Funktion angenähert werden.[6] Die nachfolgende Formel beschreibt das einfache Modell des Transistors im Pinch-Off-Bereich. IDSS und Up sind wie oben beschrieben von der Herstellung abhängige Parameter und werden im Datenblatt angegeben.

Kanallängenmodulation

Ähnlich wie bei einem MOSFET kommt es durch die Kanalabschnürung am Drain-Kontakt im pinch-off-Bereich zu einer kürzeren effektiven Leitungslänge im Transistor abhängig von der Drain-Source-Spannung. Der Grund dafür liegt in der Abnahme der Beweglichkeit durch die hohen Feldstärken am Ende des Kanals und die damit verbundene endliche Sättigungsgeschwindigkeit der Ladungsträger. Dies führt zu einem Anstieg des Sättigungsstromes im Ausgangskennlinienfeld. Stark vereinfacht kann man dies mit der Einführung einer Earlyspannung UA berücksichtigen:

Einsatzgebiete

Der JFET erzeugt gegenüber dem Bipolar-Transistor bei Frequenzen unterhalb von ca. 1 kHz eine deutlich kleinere Rauschleistung, bei höheren Frequenzen ist der Einsatz sinnvoll, wenn der Quellenwiderstand größer als ca. 100 kΩ … 1 MΩ ist (Typisch für Kondensatormikrophone, Piezoelektrische Sensoren, hochwertige Photodetektoren oder Aktivantennen mit geringer Höhe).

Für Anwendungen als Stromquelle, die so genannte Stromregeldiode, oder einstellbarer Widerstand sind vorgefertigte Typen mit abgestuften Werten erhältlich.

Weiter wird er zu Umschaltung von Signalspannungen im Nieder- und Hochfrequenzbereich (NF- und HF-Bereich), als Schaltmischer bei hohem Signalpegel und als Signaldiode mit geringem Sperrstrom verwendet.

Weiters kann mit zwei JFETs ähnlich wie bei Tunneldioden ein negativ differenzieller Widerstand realisiert werden, welche in Oszillatoren zur Schwingungserzeugung eingesetzt werden kann. Diese JFET-Schaltung wird als Lambda-Diode bezeichnet.

Bekannte Kleinsignal-Typen

- BF245A/B/C

- n-Kanal-JFET; typische Parameter: UDS ≤ 30 V; Pmax = 0,30 W; IDSS = 2…6,5 mA (A-Typ) / 6…15 mA (B-Typ) / 12…25 mA (C-Typ); Up = -0,5…−8 V; Bauform TO-92

- J310

- n-Kanal-JFET; typische Parameter: UDS ≤ 25 V; Pmax = 0,35 W; IDSS = 24…60 mA; Bauform TO-92

- MMBF4416

- n-Kanal-JFET; typische Parameter: UDS ≤ 30 V; Pmax = 0,225 W; IDSS = 5…15 mA; Bauform SOT-23

Siehe auch

- Stromregeldiode (engl. current regulation diode, CRD bzw. current limiting diode, CLD)

Weblinks

Commons: JFET – Sammlung von Bildern, Videos und Audiodateien

Commons: JFET – Sammlung von Bildern, Videos und AudiodateienEinzelnachweise

- ↑ Reinhold Paul: Feldeffekttransistoren – physikalische Grundlagen und Eigenschaften. Verlag Berliner Union, Stuttgart 1972, ISBN 3-408-53050-5.

- ↑ Bo Lojek: The MOS Transistor. In: History of Semiconductor Engineering. Springer, Berlin 2007, ISBN 978-3540342571, S. 317ff..

- ↑ The Semiconductor Data Book, Motorola Inc. 1969 AN-47

- ↑ Data & Design Manual, Teledyne Semiconductors 1981, Junction FETs in Theorie and Application

- ↑ Low Power Discretes Data Book, Siliconix incorporated 1989, Application Note LPD-1

- ↑ H. H. Meinke, F. W Gundlach: Taschenbuch der Hochfrequenztechnik – Band 1: Grundlagen. Springer-Verlag, Berlin 1992, ISBN 3540547142. S. G20

Wikimedia Foundation.

![I_\mathrm{DS} = I_\mathrm{DSS}\left[1 - \frac{U_\mathrm{GS}}{U_\mathrm{p}}\right]^2](7/837b0310d9674470b9fa82831b9f83d9.png)