- Metall-Oxid-Halbleiter-Feldeffekttransistor

-

Der Metall-Oxid-Halbleiter-Feldeffekttransistor (englisch metal oxide semiconductor field-effect transistor, MOSFET auch MOS-FET, selten MOST) gehört zu den Feldeffekttransistoren mit isoliertem Gate, auch als IGFET bezeichnet. Er ist den Metall-Isolator-Halbleiter-Feldeffekttransistoren (MISFET) zuzurechnen. Obwohl heute dotiertes Polysilizium als Gate-Material vorherrscht, blieb die Bezeichnung MOSFET beibehalten. Historisch begründet steht damit MOSFET als Synonym für IGFET (siehe auch Abschnitt Name).

Wie bei allen IGFE-Transistoren erfolgt die Ansteuerung eines MOSFETs über eine Steuerspannung (Gate-Source-Spannung) bzw. Steuerpotential (Gate-Potential), mit ihr kann der Stromfluss von Drain nach Source beeinflusst werden.

Wegen der großen Packungsdichte und der geringen Herstellungskosten handelt es sich um den meist verwendeten Transistor für analoge und digitale integrierte Schaltungen. Im Jahr 2008 wurden bis zu 1,9 Milliarden Transistoren in einem Prozessor verbaut.

Inhaltsverzeichnis

Geschichte

Historisch gesehen ist das Funktionsprinzip des MOSFETs wesentlich länger bekannt als das des Bipolartransistors. Die ersten Patentanmeldungen stammen aus den Jahren 1926 von Julius Edgar Lilienfeld[1] und 1934 von Oskar Heil. Die ersten MOSFETs wurden allerdings erst 1960 gefertigt, als mit dem Silizium/Siliziumdioxid ein Materialsystem zur Verfügung stand, mit dem sich eine reproduzierbar gute Halbleiter-Isolator-Grenzfläche herstellen ließ. Damit verbunden war die Abkehr vom Germanium als Basismaterial und steigende Anforderungen an die Fertigungsbedingungen (Reinräume, strenges Temperaturregime).

Ab Anfang bzw. Mitte 1970 kam dotiertes Polysilizium als Gate-Material zum Einsatz und verdrängte damit aufgedampftes Aluminium.[2] Seit der Jahrtausendwende wurde verstärkt an der neuartigen High-k+Metal-Gate-Technik geforscht und 2007 erstmals in der Massenproduktion eingesetzt.

Aufbau und Funktionsweise

Ein MOSFET ist ein aktives Bauelement mit mindestens drei Anschlüssen (Elektroden): G (gate, dt. Steuerelektrode), D (drain, dt. Abfluss), S (source, dt. Quelle). Bei einigen Bauformen wird ein zusätzlicher Anschluss B (bulk, Substrat) nach außen geführt. Meistens ist das Bulk jedoch intern mit der Source verbunden.

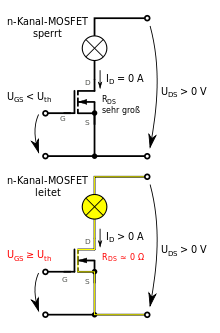

Wie andere Feldeffekttransistoren wirkt der MOSFET wie ein spannungsgesteuerter Widerstand, das heißt, über die Gate-Source-Spannung UGS kann der Widerstand zwischen Drain und Source RDS und somit der Strom IDS (vereinfacht ID) durch RDS um mehrere Größenordnungen geändert werden. Der Schlüssel zum Verständnis dieser Widerstandsänderung in einer MOS-Struktur liegt in der Entstehung (Anreicherungstypen) bzw. Zerstörung (Verarmungstypen) eines leitenden Kanals unter dem Gate (Details siehe unten).

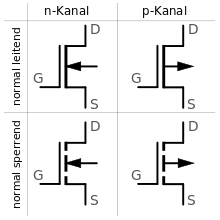

Grundtypen

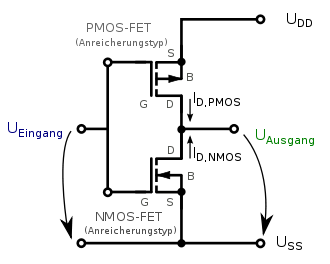

Ähnlich wie der Bipolartransistor kann auch der MOSFET in die zwei grundlegenden Varianten p-Typ (auch p-leitend, p-Kanal oder PMOS) und n-Typ (auch n-leitend, n-Kanal oder NMOS) eingeteilt werden. Werden, beispielsweise in integrierten Digitalschaltungen, beide Typen gemeinsam verwendet, spricht man von CMOS (engl.: Complementary MOS). Zusätzlich gibt es von beiden Varianten jeweils zwei Formen, die sich im inneren Aufbau und in den elektrischen Eigenschaften unterscheiden:

- Verarmungstyp (engl.: depletion) – auch selbstleitend, normal-an, normal leitend

- Anreicherungstyp (engl.: enhancement) – auch selbstsperrend, normal-aus, normal sperrend

In der Praxis werden mit großer Mehrheit Anreicherungstypen eingesetzt.

Grundsätzlicher Aufbau und physikalische Funktion

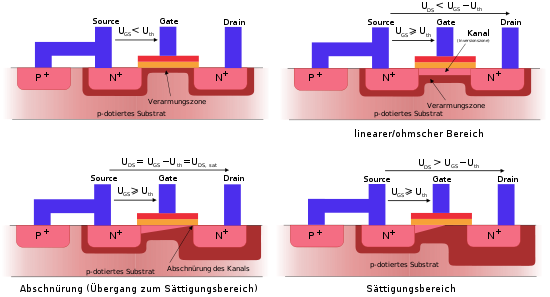

Als Beispiel sei der selbstsperrende n-Kanal-MOSFET gegeben.

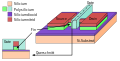

Als Grundmaterial dient ein schwach p-dotierter Siliziumeinkristall (Substrat). In dieses Substrat sind zwei stark n-dotierte Gebiete eingelassen, die den Source- bzw. Drain-Anschluss erzeugen. Zwischen den beiden Gebieten befindet sich weiterhin das Substrat, wodurch eine npn-Struktur entsteht, die vorerst keinen Stromfluss zulässt (vgl. npn-Transistor: Ohne Basisstrom ist der Transistor gesperrt). Genau über diesem verbleibenden Zwischenraum wird nun eine sehr dünne, widerstandsfähige Isolierschicht (Dielektrikum, meist Siliziumdioxid) aufgebracht. Das Dielektrikum trennt die darüberliegende Gate-Elektrode vom Silizium (genauer vom Kanalgebiet). Als Gate-Material wurde bis Mitte der 1980er Aluminium verwendet, das von n+- bzw. p+-dotiertem (entartetem) Polysilizium (Abkürzung für polykristallines Silizium) abgelöst wurde.

Durch diesen Aufbau bilden Gate-Anschluss, Dielektrikum und Bulk-Anschluss einen Kondensator, der beim Anlegen einer Spannung zwischen Gate und Bulk aufgeladen wird. Durch das elektrische Feld wandern im Substrat Minoritätsträger (bei p-Silizium Elektronen) an die Grenzschicht und rekombinieren mit den Majoritätsträgern (bei p-Silizium Defektelektronen). Das wirkt sich wie eine Verdrängung der Majoritätsträger aus und wird „Verarmung“ genannt. Ab einer bestimmten Spannung Uth (engl. threshold voltage, Schwellspannung) ist die Verdrängung der Majoritätsladungsträger so groß, dass sie nicht mehr für die Rekombination zur Verfügung stehen. Es kommt zu einer Ansammlung von Minoritätsträgern, wodurch das eigentlich p-dotierte Substrat nahe an der Isolierschicht n-leitend wird. Dieser Zustand wird starke „Inversion“ genannt. Der entstandene dünne n-leitende Kanal verbindet nun die beiden n-Gebiete Source und Drain, wodurch Ladungsträger (beinahe) ungehindert von Source nach Drain fließen können.

Prinzipiell sind Source- und Drain-Anschluss zunächst gleichwertig, meist ist der Aufbau aber nicht symmetrisch, um ein besseres Verhalten zu erzielen. Außerdem wird bei den meisten Bauformen Bulk intern mit Source verbunden, da ein Potentialunterschied zwischen Source und Bulk die Eigenschaften des Transistors (vor allem die Schwellenspannung) negativ beeinflusst (body effect). Auf die grundlegende Funktion hat die Verbindung keinen Einfluss. Allerdings entsteht nun zusätzlich eine Diode zwischen Source- und Drain-Anschluss, die parallel zum eigentlichen Transistor liegt (Bulk mit dem p-dotierten Substrat und Drain mit dem n-Gebiet bilden den p-n-Übergang). Diese sogenannte Body-Diode ist als Pfeil im Schaltsymbol des MOSFETs dargestellt und zeigt beim n-Kanal-MOSFET vom Bulk-Anschluss zum Kanal. Bei der Anwendung ist die Body-Diode in der Regel in Sperrrichtung gepolt, bei manchen Schaltanwendungen kann sie jedoch genutzt werden, um Inversbetrieb zu verhindern. Sie kann den vollen Drain-Strom des MOSFETs führen, schaltet aber relativ langsam, so dass für schnelle Schalter externe Dioden benutzt werden.

Siehe auch: FeldeffekttransistorVarianten im Aufbau

Neben den konventionellen MOSFET-Varianten existieren noch diverse Spezialvarianten mit verändertem Aufbau. Ziel ist ein besseres Schaltungverhalten, was jedoch mit zum Teil deutlich erhöhtem Herstellungsaufwand verbunden ist. Beispiele sind der VMOS-FET oder der FinFET, wobei letzterer den Vorteil eines vergrößerten Kanalbereichs bietet; aufgrund der Kanalbereiche oft auch als Dual- (Tetrode) oder Tri-Gate bezeichnet.[3][4] Diese werden zum Beispiel in HF-Schaltungen eingesetzt (HF-Verstärker, multiplikativer Mischer).

-

Prinzipieller Aufbau eines n-Kanal-MOSFETs im Querschnitt (Planartechnik)

Zuordnung der Source- und Drain-Gebiete bei PMOS und NMOS

Source bezeichnet den Anschluss, von dem die für den Ladungstransport verantwortlichen Ladungsträger (Majoritätsladungsträger) im leitenden Fall in Richtung des Drain-Anschlusses driften.

Beim p-Kanal-MOSFET bilden Defektelektronen (Löcher) die Majoritätsladungsträger, sie fließen in Richtung der technischen Stromrichtung. Bei der Beschaltung von p-Kanal-MOSFET ist das Source-Potential φS (+, näher an UDD gelegen) größer als das Drain-Potential φD (−; näher an USS gelegen)

Beim n-Kanal-MOSFET bilden hingegen Elektronen die Majoritätsladungsträger. Sie fließen entgegen der technischen Stromrichtung. Bezüglich des elektrischen Potentials ist daher die Lage von Source und Drain entgegengesetzt zum p-Kanal-MOSFET. Das heißt, das Source-Potential φS (−; näher an USS gelegen) ist geringer als das Drain-Potential φD (+; näher an UDD gelegen).

Kennlinienfeld

Aktive Spannungen und Versorgungsspannungen Symbol Berechnung Beschreibung UDS φD − φS Ausgangsspannung zwischen Drain und Source. UGS φGate − φS Eingangsspannung zwischen Gate und Source. USB φS − φBulk Spannung zwischen Source und Back-Gate (auch Bulk-Anschluss genannt). UDD positive Versorgungsspannung (aus NMOS-Technik, wird auch in CMOS verwendet) USS negative Versorgungsspannung (aus NMOS-Technik, wird auch in CMOS verwendet) Schwellenspannung

Die Schwellenspannung Uth (engl.: threshold voltage) stellt ein zentrales Element bei der Modellbetrachtung von MOSFETs dar und hängt stark von der Prozesstechnik ab. Dabei entscheiden die Dotierungen von Source, Drain und des Kanalgebietes über die Größe der Schwellenspannung.

für NMOS-Verarmungstyp und PMOS-Anreicherungstyp

für NMOS-Verarmungstyp und PMOS-Anreicherungstyp für NMOS-Anreicherungstyp und PMOS-Verarmungstyp, typ. zwischen 1V und 3V.

für NMOS-Anreicherungstyp und PMOS-Verarmungstyp, typ. zwischen 1V und 3V.

Zudem ist die Schwellenspannung abhängig von der Temperatur. Für die Beschreibung reicht die Abhängigkeit 1. Ordnung (lineare Abhängigkeit):

wobei α der Temperaturkoeffizent und T0 die Stütztemperatur (beispielsweise die typische Betriebstemperatur) ist.

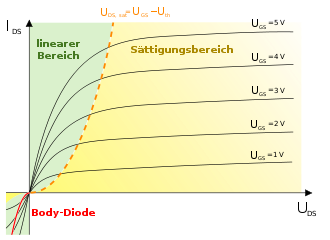

Ausgangskennlinienfeld

Die Darstellung der Zusammenhänge zwischen dem Drain-Strom ID und der Drain- Source-Spannung UDS in Abhängigkeit von der Gate-Source-Spannung UGS wird als Ausgangskennlinienfeld eines MOSFETs bezeichnet. Es ist für alle MOSFETs (NMOS-Anreicherungstyp, NMOS-Verarmungstyp, PMOS-Anreicherungstyp und PMOS-Verarmungstyp) prinzipiell gleich. Unterschiede ergeben sich nur in den Potentialbezugspunkten von Drain und Source, sowie im Vorzeichen des Verstärkungsfaktors. Die Kennlinien werden durch weitere Effekte (Temperatur, Substratvorspannung, Kurzkanaleffekte etc.) beeinflusst.

Die einzelne ID-UDS-Kennlinie eines MOSFETs unterteilt sich in drei Bereiche: den Sperrbereich, den aktiven Bereich und den Sättigungsbereich.

Sperrbereich

Im Sperrbereich (auch Abschaltbereich oder Subthreshold-Bereich genannt, engl. cutoff region) liegt die Gate-Source-Spannung UGS unterhalb der Schwellenspannung Uth.

Für

gilt:

gilt:In einfachen Modellen (z. B. im „SPICE level 1“-Modell) wird

angenommen.

angenommen.Der Leckstrom (engl.: leakage current) eines Anreicherungs-MOSFET (engl.: enhancement MOSFET) berechnet sich aus der Gleichung für den Sperrbereich

(nur für NMOS-Anreicherungs- und PMOS-Anreicherungs-Typ)

(nur für NMOS-Anreicherungs- und PMOS-Anreicherungs-Typ)

Linearer Bereich

Im linearen Bereich (auch Triodenbereich oder ohmscher Bereich genannt, engl.: (triode region oder ohmic region)) liegt die Gate-Source-Spannung UGS über der Schwellenspannung Uth (Im Fall des Anreicherungs-MOSFET), sodass ein durchgehender Kanal zwischen Drain und Source entsteht. Der Bereich wird durch die Kennlinie der Grenzspannung UDS,sat = UGS − Uth begrenzt.

Die Bezeichnung stammt von dem Umstand, dass die Kennlinien bei

nahezu linear durch den Ursprung verlaufen, was dem Verhalten eines ohmschen Widerstands entspricht.

nahezu linear durch den Ursprung verlaufen, was dem Verhalten eines ohmschen Widerstands entspricht.Für

und

und  gilt:

gilt:Sättigungsbereich

Im Sättigungsbereich (engl. saturation region, active mode, auch Abschnürbereich oder aktiver Bereich zur Vermeidung von Verwirrung mit dem Sättigungsbereich bei Bipolartransistoren genannt) verläuft die ID-UDS-Kennlinie parallel zur UDS-Achse. Real steigt der Drainstrom ID aber weiterhin an (siehe Kanallängenmodulation).

Beim Vergleich mit einem Bipolartransistor muss bei der Verwendung des Begriffs Sättigungsbereich darauf geachtet werden, dass der Begriff Sättigung beim Bipolartransistor eine andere Bedeutung hat.

Für

und

und  gilt:

gilt:Kennlinieneffekte

Verwendete Formelzeichen Zeichen und Formel Beschreibung

Flächenbezogene Kapazität des Oxids

Kapazität des Oxids

Verarmungskapazität. (engl.: depletion capacitance), diese setzt sich aus den Überlappkapazitäten an Drain und Source zusammen

Absolute Dielektrizitätszahl im Vakuum

relative Dielektrizitätszahl von Siliziumdioxid (häufig verwendet)

Oxiddicke

Gate-Breite

Gate-Länge

Schwellenspannungsstrom (engl.: threshold current)

Boltzmannkonstante

Verstärkungsfaktor (NMOS)

Verstärkungsfaktor (PMOS)

Beweglichkeit der Elektronen (NMOS)

Beweglichkeit der Löcher (PMOS)

Temperaturspannung bei T = 295 K

subthreshold swing (Kehrwert von subthreshold slope) Substratvorspannung, Back-Gate-Steuerung, Body-Effekt

Wenn eine Substratvorspannung (auch Back-Gate-Spannung) an den Transistor angelegt wird, so hängt die Schwellenspannung von der Source-Bulk-Spannung ab. Je größer die Spannung USB wird, desto größer wird die Schwellenspannung.

mit:

- Substrateffekt-Parameter:

- Oberflächenpotential bei starker Inversion:

- Dotierungskonzentration im Substrate bzw. in der n- oder p-Wanne: NSubstrat

- Eigenleitkonzentration (Silizium):

bei T = 295 K

bei T = 295 K  mit

mit

Kanallängenmodulation

Unter dem Begriff Kanallängenmodulation wird ein Effekt verstanden, dessen Auswirkungen dem Early-Effekt der Bipolartransistoren ähneln.

Die Kanallängenmodulation tritt im Sättigungsbereich auf und modelliert die Einschnürung des Kanales (der Kanal erreicht das Drain nicht mehr, die Region ohne Kanal wird auch Pinch-Off-Region genannt).

In der Ausgangskennlinie ist die Kanallängenmodulation durch den Anstieg des Drainstromes im Sättigungsbereich bei zunehmender Drain-Source-Spannung zu erkennen.

Spürbare Auswirkungen zeigt die Kanallängenmodulation bei Strukturgrößen von L < 1 µm. In Näherung lässt sich diesem Effekt durch folgende Näherungsgleichung Rechnung tragen, wobei λ das Ausmaß charakterisiert:

Um die Stetigkeit zwischen den Arbeitsbereichen zu erhalten, wird der Kanallängenmodulationsfaktor in jedem Arbeitsbereich multipliziert.

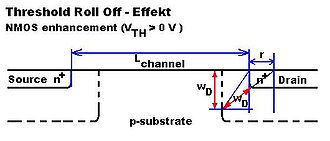

„Threshold-Voltage-roll-off“-Effekt

Bei kurzen Kanälen beeinflusst ein Effekt höherer Ordnung die Schwellenspannung, dieser wird „Threshold-Voltage-roll-off“-Effekt genannt. Dabei beeinflusst die Kanallänge die Schwellenspannung:

- Weite der Raumladungszone am Drain:

- Oberflächenpotential bei starker Inversion:

- Dotierungskonzentration im Substrate bzw. in der n- oder p-Wanne: NSubstrat

- Dotierungskonzentration für intrinsisches Silizium:

bei T = 295 K

bei T = 295 K - Permittivität

mit

mit

Schaltbetrieb

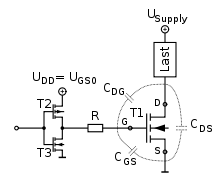

Beim Schalten eines MOSFETs wirken sich primär die Streukapazitäten innerhalb des Bauteils auf das zeitliche Verhalten aus. Wesentlichen Einfluss auf die Schaltzeiten besitzt die sogenannte Miller-Kapazität, welche zwischen der Gate-Elektrode zur Drain-Elektrode entsteht. Für die Modellbetrachtung des Schaltverhaltens dienen die Parameter CGS, CDS und CDG (siehe Bild), wohingegen in Datenblättern Ciss, Coss und Crss angegeben sind. Das liegt daran, dass letztere einfach messbare Größen darstellen. Nachfolgende Formeln ermöglichen die Umrechnung zwischen beiden Systemen:

(Für die Ansteuerung von Leistungs-MOSFETs empfiehlt sich wegen der „parasitären Kapazitäten“ immer eine Gegentakt-Ansteuerung.)

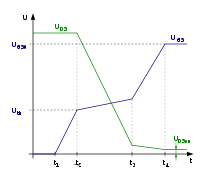

Der Einschaltvorgang teilt sich in drei Abschnitte auf (siehe auch Bild unten):

- t1 < t < t2: Gate-Source-Kapazität aufladen (Totzeit)

- t2 < t < t3: Miller-Kapazität entladen

- t3 < t < t4: Gate-Source-Kapazität aufladen und voll durchschalten

Während der ersten Phase steuert der MOSFET noch nicht durch, denn zunächst muss die Gate-Source-Kapazität bis zum Erreichen der Schwellspannung aufgeladen werden. Ab dem Punkt t2 beginnt die Drain-Source-Strecke durchzusteuern. Dabei muss der Treiber auch den Entladestrom für die Drain-Gate-Kapazität abführen. Dabei stellt sich ein Gleichgewicht ein, denn je höher UGS steigt, desto schneller fällt UDS und damit UDG, wodurch ein höherer Entladestrom fließt. Die Gate-Source-Spannung bildet zeitlich ein Plateau, weil die Drain-Gate-Spannung einem weiteren Anstieg entgegenarbeitet. Die Stärke dieses Effektes hängt folglich direkt mit der Höhe der Versorgungsspannung zusammen. Bei Brückenschaltungen verwendet man oft eine Bootstrap-Schaltung, um den notwendigen Mindestwert von UGS sicherzustellen.

für t2 < t < t3

für t2 < t < t3

Die letzte Phase sorgt für das vollständige Durchschalten des Transistors, damit ein minimaler RDSon erreicht wird. Dadurch verringern sich die ohmschen Verluste, und ein hohes On/Off-Verhältnis, sprich ein hoher Wirkungsgrad, wird erzielt.

Der Ausschaltvorgang verläuft umgekehrt, jedoch sind die Zeiten nicht identisch. Die Ausschaltzeit ist dabei immer etwas länger als die Einschaltzeit, was häufig in Leistungs-Gegentakt-Endstufen durch entsprechende Totzeiten in der Ansteuerung berücksichtigt werden muss.

Das gezeigte Modell stellt eine starke Vereinfachung dar und dient dem grundlegenden Verständnis für das Schaltverhalten eines MOSFETs, was für viele Anwendungen auch hinreichend ist. Für detaillierte Betrachtungen muss die Spannungsabhängigkeit der Kapazitäten herangezogen werden[6] sowie die Auswirkung weiterer „parasitärer Bauelemente“. Statt der Gate-Source-Kapazität wird die Gate-Ladung QG betrachtet.

Siehe auch: Kenngrößen von Leistungs-MOSFETsBodydiode

Bestimmte Schaltanwendungen, z. B. Brückenschaltungen, sind so konzipiert, dass die Bodydiode anspricht. Allerdings bereiten die langsame Rückwärtserholzeit und die hohe Flussspannung gelegentlich Probleme, so dass dann extern eine schnelle Schottkydiode (in Sperrrichtung zur Betriebsspannung) parallel an Source und Drain hinzugefügt wird, deren Flussspannung dazu geringere Werte aufweist. Dadurch bleibt der Strom über die Bodydiode klein und negative Effekte treten hier kaum auf. Außerdem wird die Gesamtverlustleistung des Transistors verringert.

Bei FREDFETs zeigt die Bodydiode besseres Schaltverhalten und ermöglicht somit einen kompakteren Aufbau.

Leckströme

Bei den Leckströmen handelt es sich um unerwünschte Stromflüsse innerhalb der Transistoren. Diese treten sowohl im gesperrten als auch im leitenden Zustand des Transistors auf. Momentan (Stand 2008) sind hier vor allem der Subthreshold-Leakage (frei übersetzt: Unterschwellspannungsleckstrom), Junction-Leakage als auch der Gate-Oxid-Leckstrom dominierend.

In konventionellen CMOS-Techniken mit Siliziumdioxid als Dielektrikum stellen die Leckströme eines der Hauptprobleme beim Chipentwurf dar, wenn Transistoren mit Gatelängen von weniger als 100 nm verwendet werden (praktisch alle 2010 aktuellen Prozessoren).[7]. So dass Mitte der 2000er Jahre bei Prozessoren im High-End-Bereich die Leckströme bis zur Hälfte des Gesamtenergieverbrauchs verursachten.[8][9] Einen Ausweg die Leckströme zu reduzieren ist die sogenannte High-k+Metal-Gate-Technik, bei der dielektrische Materialien mit hoher Permittivität (High-k-Dielektrikum) statt Siliziumdioxid genutzt werden, beispielsweise dotiertes Hafniumoxid.

Bauformen

Im Wesentlichen ist zwischen lateralen (also parallel zu der Oberfläche ausgerichteten) und vertikalen Bauformen zu unterscheiden. Während laterale Transistoren vorwiegend in der Nachrichtentechnik zum Einsatz kommen (lateral double-diffused MOSFET, LDMOS[10]), findet sich die vertikale Bauform überwiegend in der Leistungselektronik wieder. Der Vorteil der vertikalen Struktur liegt in der höheren möglichen Sperrspannung der Bauelemente.

Vor- und Nachteile

Ein prinzipieller Nachteil der MOSFET-Technik ist die geringe Oberflächenbeweglichkeit der Ladungsträger im Kanal. Elektronen besitzen dabei eine höhere Beweglichkeit als Defektelektronen, daher haben n-Kanal-MOSFET bessere Eigenschaften als p-Kanal-Typen. Durch die Verkleinerung der Bauelementstrukturen lässt sich dieser Nachteil jedoch ausgleichen und die Schaltgeschwindigkeit erhöht sich. Dadurch gelingt es einerseits, schnellere Einzeltransistoren herzustellen, andererseits lassen sich durch feine Wabenstrukturen auch schnelle MOSFET für große Ströme herstellen. Durch Skalierung in den Submikrometerbereich wird der MOSFET für integrierte digitale Anwendungen mit Taktfrequenzen oberhalb von 1 GHz verwendbar. MOSFETs sind wegen ihres einfachen Herstellungsprozesses (CMOS-Prozess) und der lateralen Struktur besonders für integrierte Schaltungen geeignet.

Da bei IGFETs im Gegensatz zu Bipolartransistoren die Steuerung nicht über einen Stromfluss (Basisstrom), sondern über eine Steuerspannung erfolgt, werden sie täuschenderweise als „stromlos“ bezeichnet. Im statischen Betrieb, d. h., bei konstanter Gate-Spannung, fließt über das Gate so gut wie kein Strom. Allerdings ist zur Umladung der Gate-Kapazität ein teilweise erheblicher Lade- und Entladestrom notwendig – in der Leistungselektronik bis über 10 A. Diese Ströme verursachen zusammen mit den Gate-Leckströmen, die bei heutigen Mikroprozessoren nicht mehr vernachlässigbar sind, die hohe Leistungsaufnahme moderner integrierter Schaltkreise.

In Leistungsanwendungen ist der sogenannte Leistungs-MOSFET hinsichtlich kurzer Schaltzeiten und geringer Schaltverluste den Bipolartransistoren und IGBTs überlegen. Er erreicht jedoch nicht deren hohe Sperrspannungen. Gegenüber bipolarer Technik besitzt die Drain-Source-Strecke des MOSFET eine reine Widerstandscharakteristik, die den statischen Spannungsabfall und die statische Verlustleistung im Betrieb bestimmt. Erst dadurch werden die hohen Wirkungsgrade von leistungselektronischen Schaltungen besonders bei niedrigen Spannungen und Batteriebetrieb möglich (vgl. Synchrongleichrichter).

Im Gegensatz zu bipolaren Transistoren besitzt der Kanalwiderstand der Drain-Source-Strecke des MOSFET einen positiven Temperaturkoeffizienten. Das bedeutet, dass bei steigender Temperatur auch der Widerstand steigt. Dadurch kann man in einigen Anwendungen mehrere MOSFETs ohne zusätzliche symmetrierende Maßnahmen parallelschalten, um die Stromtragfähigkeit zu erhöhen und den Spannungsabfall zu verringern. Sobald einer der MOSFETs durch zu viel Strom zu heiß wird, steigt sein Widerstand. Dadurch teilt sich die Strombelastung der MOSFETs gleichmäßig auf.

Leistungs-MOSFETs auf Siliziumbasis werden vorteilhaft beim Schalten von Spannungen bis ca. 800 V und Strömen von bis zu mehreren 100 A eingesetzt. Einsatzgebiete sind u. a. Schaltnetzteile, Synchrongleichrichter, getaktete Strom- und Spannungsregler und auch starke Hochfrequenzsender bis in den UKW-Bereich. In Sonderanwendungen werden Schaltzeiten von nur einigen Nanosekunden bei Spannungen von mehreren Kilovolt durch Reihenschaltung realisiert.

Handhabung

MOSFETs weisen durch die sehr hochohmige Isolierung des Gates gegenüber dem Source-Drain-Kanal eine große Empfindlichkeit gegenüber elektrostatischen Entladungen (engl. electro-static discharge, ESD) auf. Das führt bei unsachgemäßer Handhabung von elektronischen Bauteilen, die aus Feldeffekttransistoren bestehen, zu einem Durchbruch der Gate-Isolierschicht und damit zur Zerstörung der Feldeffekttransistoren. Die daraus resultierenden Schwierigkeiten bei der Handhabung waren einer der Gründe, warum Feldeffekttransistoren sich gegenüber Bipolartransistoren erst einige Jahrzehnte später am Markt durchsetzen konnten. Vielfach konnten schützende Drahtbrücken zwischen Gate und Source (Drain, Bulk) erst nach Einlötung des MOSFETs in der Anwendungsschaltung entfernt werden. Prinzipiell sind jedoch Leistungs-MOSFETs auf Grund ihrer meist im Nanofaradbereich liegenden Gatekapazität ausreichend gegen elektrostatische Aufladung natürlich geschützt, so dass besondere Schutzmaßnahmen – wie externe Drahtbrücken – hier meist nicht mehr benötigt werden. Heutige diskrete Kleinleistungs-Feldeffekttransistoren und integrierte Schaltungen haben außerdem meist integrierte Schutzdioden mit Widerständen oder entsprechende Halbleiterstrukturen an den Anschlussleitungen, welche die Auswirkungen von elektrostatischen Entladungen auf die empfindliche Gate-Isolierschicht minimieren. Trotzdem müssen bei der Handhabung von Feldeffekttransistoren immer noch besondere Vorsichtsmaßnahmen zur Vermeidung von elektrostatischen Aufladungen getroffen werden. So sind beispielsweise Arbeits- und Fertigungsbereiche, in denen mit Feldeffekttransistoren gearbeitet wird, durch ESD-Warnschilder gekennzeichnet. Zusätzlich sind immer die Herstellerangaben zu beachten.

Name

Derzeit (2009) werden bei handelsüblichen CMOS-Schaltkreisen noch Polysilizium (Gate-Material) und Siliziumdioxid (Isolator zwischen dem Gate und dem Kanal) eingesetzt. Da kein Metall verwendet wird, ist die Bezeichnung MOSFET nicht mehr korrekt. Sie ist eher historisch entstanden – Die Bezeichnung stammt eigentlich aus der Zeit (bis Anfang der 1980er), als Aluminium (ein Metall) als Gate-Material verwendet wurde – und wird immer noch synonym verwendet.

In der Halbleitertechnik gibt es allerdings derzeit Bestrebungen, das Polysilizium gegen andere Materialien wie Übergangsmetalle auszutauschen. Außerdem werden wahrscheinlich in zukünftigen integrierten Schaltungen zunehmend sogenannte High-k-Materialien anstelle von Siliziumdioxid als Gate-Dielektrikum sowie Metalle als Gate-Elektrode eingesetzt (vgl. High-k+Metal-Gate-Technik). Damit würde in einigen Fällen die Bezeichnung MOSFET wieder vollkommen richtig sein, dennoch ist es oft günstiger, die neutrale Bezeichnung MISFET (Metall-Nichtleiter-Halbleiter-FET) oder ganz allgemein IGFET (FET mit isoliertem Gate) zu verwenden.

Siehe auch

Weblinks

Commons: MOSFET – Sammlung von Bildern, Videos und Audiodateien

Commons: MOSFET – Sammlung von Bildern, Videos und Audiodateien- Java-Applet zu NMOS

- Elektronik-Kompendium - MOS-Feldeffekttransistor (MOS-FET)

- Computer History Museum: [1]. Auf: computerhistory.org.

Literatur

- Hans-Joachim Fischer, Wolfgang E. Schlegel: Transistor- und Schaltkreistechnik. 4. Auflage. Militärverlag der DDR, Berlin 1988.

- Hans-Günther Wagemann, Tim Schönauer: Silizium-Planartechnologie. Grundprozesse, Physik und Bauelemente. Teubner, Stuttgart/Leipzig/Wiesbaden 2003, ISBN 3-519-00467-4.

Einzelnachweise

- ↑ Patent US1745175: Method and Apparatus For Controlling Electric Currents. Erfinder: J. E. Lilienfeld (PDF).

- ↑ Sami Franssila: Introduction to Microfabrication. John Wiley and Sons, 2010, ISBN 9780470749838, S. 229.

- ↑ D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T. J. King, J. Bokor, C. Hu: FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. In: Electron Devices, IEEE Transactions on. 47, Nr. 12, 2000, S. 2320-2325, doi:10.1109/16.887014 (PDF).

- ↑ E.J. Nowak, I. Aller, T. Ludwig, K. Kim, R.V. Joshi, Ching-Te Chuang, K. Bernstein, R. Puri: Turning silicon on its edge – double gate CMOS/FinFET technology. In: Circuits and Devices Magazine, IEEE. 20, Nr. 1, 2004, S. 20–31, doi:10.1109/MCD.2004.1263404.

- ↑ Carl Walding: Nicht nur Verluste minimiert. elektroniknet.de. Abgerufen am 20. September 2008.

- ↑ Martin Stiftinger: Simulation und Modellierung von Hochvolt-DMOS-Transistoren. Dissertation, TU Wien, 1994.

- ↑ Gordon Moore: No Exponential is Forever … but We Can Delay ’Forever’. International Solid State Circuits Conference (ISSCC), USA, 2003

- ↑ Y. S. Borkar: VLSI Design Challenges for Gigascale Integration. '18th Conference on VLSI Design, Kolkata, India, 2005

- ↑ ITRS – International technology roadmap for semiconductors 2006 Update.Technischer Report, 2006

- ↑ Microwave Encyclopedia, Micorowaves101.com: LDMOS, abgerufen am 29. Nov. 2008

Wikimedia Foundation.