- Halbleitertechnik

-

Die Halbleitertechnik definiert sich historisch und aufgrund der Verwendung der Produkte als Schlüsselkomponenten in elektrotechnischen Erzeugnissen als Teilgebiet der Elektrotechnik (speziell der Mikroelektronik). Trifft man die Zuordnung aufgrund der eingesetzten Methoden und Verfahren und materialtechnischen Eigenschaften der hergestellten Produkte, so ist auch eine Zuordnung zu den Bereichen Chemietechnik und Keramik möglich und folgerichtig.

Die Halbleitertechnik befasst sich mit der technischen Herstellung mikroelektronischer Bauelemente und mikroelektronischer Baugruppen (Integrierte Schaltungen) vorwiegend aus Halbleitermaterialien.

Inhaltsverzeichnis

Einleitung

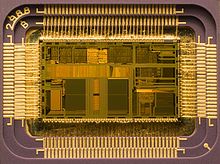

Integrierter Schaltkreis. Das Chip-Gehäuse wurde geöffnet und ermöglicht den Blick auf den eigentlichen Halbleiter. Die erkennbaren Strukturen im Zentrum sind die realisierte elektronische Schaltung. Im Außenbereich sind die goldenen Anschlussleitungen zu erkennen, welche die elektrische Verdrahtung zwischen IC und den Gehäusekontakten bildet.

Integrierter Schaltkreis. Das Chip-Gehäuse wurde geöffnet und ermöglicht den Blick auf den eigentlichen Halbleiter. Die erkennbaren Strukturen im Zentrum sind die realisierte elektronische Schaltung. Im Außenbereich sind die goldenen Anschlussleitungen zu erkennen, welche die elektrische Verdrahtung zwischen IC und den Gehäusekontakten bildet.

Die von der Halbleitertechnik eingesetzten Verfahren sind weitgehend chemischer Natur. Physikalische Methoden werden unterstützend eingesetzt (Lithographie, Implantation, Planarisieren, Messtechnik)

Der überwiegende Teil der Bauelemente wird derzeit im Planarverfahren (Jean Hoerni – Realisierung mehrerer Schaltungsbestandteile in einem Substrat durch selektive Dotierung) hergestellt. Die folgende Beschreibung bezieht sich auf dieses Verfahren.

Die Funktion des mikroelektronischen Bauelements wird meist auf der Oberfläche eines Einkristalls aus Halbleitermaterial realisiert, indem man in mehreren aufeinanderfolgenden Schritten auf das Basismaterial Schichten mit spezifischen elektrischen Eigenschaften (Schichten mit bestimmter Leitfähigkeit, Isolierschichten und Leiterbahnen) übereinander aufbringt. Durch die unterschiedlichen Eigenschaften der Einzelschichten entstehen in der Schichtfolge Transistorfunktionen, Kondensatoren, Widerstände und auch andere Bauelemente.

Aus der Kleinheit, d. h., der Strukturgröße mikroelektronischer Bauelemente resultieren spezielle Anforderungen an das Fertigungsverfahren. So wird Partikelfreiheit im eigentlichen Herstellungsprozess und Staubfreiheit in der Fertigungsumgebung gefordert (Reinraumherstellung).

In der Praxis wird häufig mit zwei verschiedenen Sichtweisen auf die Halbleitertechnik geschaut:

- Die Einzelprozess-Sicht: hierbei werden die struktur- oder eigenschaftsändernden Verfahren an sich betrachtet unter dem Aspekt, welche Parameter der Prozesse zu den gewünschten physikalischen Eigenschaften (Dimension, Leitfähigkeit, Homogenität, usw.) führen

- Die Integrationssicht: in diesem Fall wird zunächst die zu realisierende Struktur – eine Transistorebene oder eine Leitungsebene – betrachtet unter dem Aspekt, welche Einzelprozesse zu den gewünschten elektrischen (oder seltener: mechanischen bzw. optischen) Eigenschaften der Struktur führen

Herstellungsprozesse

Die einzelnen Elemente der mikroelektronischen Schaltungen werden auf einem Halbleitersubstrat, meist einem sogenannten Wafer, durch Dotierung/Legierung des Substratmaterials und durch gezieltes Aufbringen funktionaler Materialschichten erzeugt.

Vorbereitung des Ausgangsmaterials

Im engeren Sinn wird die Herstellung des Ausgangsmaterials nicht unter Halbleitertechnik gefasst, soll hier aber zur Vollständigkeit beschrieben werden: Bei der Gewinnung von Halbleitermaterialien (Silizium, Germanium, Verbindungshalbleiter wie Gallium-Arsenid und Siliziumgermanium) werden durch chemische und chemisch-metallurgische Verfahren hochreine Einkristallsubstrate erzeugt (in wenigen Fällen, z. B. für Solarzellen, sind auch polykristalline Substrate im Einsatz). Um die einwandfreie Funktion der später zu realisierenden Bauteile zu gewährleisten, ist ein qualitativ sehr hochwertiges Substratmaterial erforderlich. Angestrebt wird ein möglichst fehlerfrei kristallisiertes, reines, homogenes Basismaterial. Sind diese Anforderungen nicht erfüllt, so können z. B. bei einzelnen Transistoren zufällig erhöhte Leckströme oder veränderte Arbeitspunkte auftreten. Auf Metallverunreinigungen liegt ein besonderes Augenmerk. Die Verunreinigungsniveaus liegen hier in Bereichen von Milliardstel (ppb-Bereich) oder Billionstel (ppt-Bereich).

Im Fall von Silizium wird aus einer mehrfach gereinigten Schmelze ausgehend von einem Keimkristall ein Zylinder von heute (2007) bis zu 300 mm Durchmesser und mehr als einem Meter Länge gezogen (siehe Czochralski-Verfahren und Zonenschmelzverfahren). Der Zylinder wird in Scheiben (Wafer) mit einer Dicke kleiner einem Millimeter zersägt, die anschließend geschliffen und poliert werden. In dieser Form findet das Halbleitermaterial üblicherweise Eingang in die eigentliche Fertigung der Bauelemente. Vor allem in den Fertigungsstätten (sogenannte „Fabs“) werden die Wafer dann in sogenannte FOUP-Kassetten (von engl.: front opening unified pod) transportiert; für den Transport außerhalb vollautomatischer Fertigungsanlagen werden so genannte FOSB-Kassetten (von engl.: front opening shipping box) eingesetzt.

Zu den weltweit größten Herstellern von Siliziumwafern zählt das deutsche Chemieunternehmen Wacker/Siltronic.

Definition der Strukturen

Um auf dem Substrat verschiedene Bauteile und Schaltungselemente realisieren zu können, müssen auf dem Ausgangsmaterial Gebiete definiert werden, die vom folgenden Prozessschritt betroffen sind und solche, die nicht betroffen sind. Dazu wird die Fotolithografie – ein fotografisches Verfahren – eingesetzt (vereinfachte Darstellung):

- Auf dem Wafer wird zunächst ein lichtempfindlicher Fotolack aufgeschleudert (Rotationsbeschichtung, engl.: Spin-coating).

- In einem Stepper oder Scanner wird das Abbild einer Maske durch Belichtung mit streng monochromatischem Licht (heute meist aufgeweiteter Laserstrahl) auf den lichtempfindlichen Fotolack übertragen. Scanner ermöglichen es, kleinere Strukturen auf den Wafer zu belichten, als es mit dem Stepper möglich ist. Der Grund dafür ist, dass beim Stepper die gesamte Fotomaske als rechteckiges Bild abgebildet wird und sich alle nicht korrigierbaren Fehler des optischen Linsensystems negativ auswirken.

Beim Scanner wird anstatt der gesamten Fotomaske nur ein schmaler Streifen im optischen Linsensystem abgebildet. Durch eine synchronisierte Bewegung von Fotomaske und Wafer wird die gesamte Fotomaske auf den Wafer belichtet.

- In einem chemischen Bad wird der Fotolack entwickelt, das heißt, die belichteten Bereiche (beim sogenannten Positivlack) des Lacks werden herausgelöst, nur die unbelichteten Bereiche verbleiben auf dem Wafer. Bei Negativlack ist es gerade umgekehrt. Hier werden die unbelichteten Stellen herausgelöst. Durch eine anschließende Wärmebehandlung (sogenanntes Hard- oder Softbake) werden die Lackstrukturen stabilisiert und Reste von Lösemitteln werden ausgetrieben.

Damit sind die Teile des Wafers durch den Fotolack abgedeckt, die durch die folgenden Prozessschritte unverändert bleiben.

- Es folgt ein halbleitertechnischer Prozessschritt – Dotieren, Abscheiden, Ätzen

- Im anschließenden Prozessschritt wird der unbelichtete Fotolack ebenfalls entfernt – das kann durch nasschemische Verfahren oder durch Veraschung im Sauerstoff-Plasma erfolgen.

Die Strukturübertragung mittels Fotolithografie – einer der teuersten Prozessschritte in der Halbleiterherstellung – ist eine entscheidende Herausforderung in der traditionellen, auf Steigerung der Integrationsdichte durch Verkleinerung setzenden Planarhalbleitertechnik. Die Gesetze der Optik begrenzen hier schon heute die Möglichkeit zur weiteren Strukturverkleinerung. Daneben stößt man inzwischen aber auch bei anderen Prozessschritten an z. B. materialbedingte Grenzen. So erlauben z. B. die elektrischen Eigenschaften bestimmter im Halbleiterprozess eingesetzter Standardmaterialen keine weitere Strukturverkleinerung. Auch die Querschnittsverkleinerung der Leiterbahnen führt zu Materialproblemen (Diffusion, Elektromigration, u. a.)

Einen temporären Ausweg bietet die Verwendung neuer Strukturmaterialien wie z. B. der Einsatz spezieller Legierungen im Leiterbahnbereich oder der Einsatz modifizierter Dielektrika (low-k- und high-k-Materialien), da hierdurch grundsätzliche Veränderungen in der Technik zunächst vermeidbar sind. Langfristig erscheint jedoch der Übergang von der planaren zu 3-dimensionalen Techniken (vertikale und horizontale Positionierung einzelner Bauelemente) unabdingbar, da hierdurch im Prinzip bei gleicher Bauteildimensionierung höhere Bauteilpackungsdichten realisierbar sind. Erste Schritte in Richtung 3D-Techniken werden derzeit gemacht (siehe z. B. DRAPA).

Dotieren des Ausgangsmaterials

Um die elektrischen Eigenschaften eines Halbleiters in bestimmten Regionen zu ändern, werden lokal Fremdatome in das Material eingebracht (Dotierung). Dies geschieht durch Ionenimplantation oder Diffusion. Die Fremdatome werden dabei in verschiedenen Tiefen und in unterschiedlichen regionalen Konzentrationen eingelagert.

- Tiefe Schichten mit geringer vertikaler Ausdehnung können dazu dienen, einzelne Transistoren in eine Isolationswanne zu legen, um sie so bezüglich ihrer Substratanschlüsse zu entkoppeln.

- Tiefe Schichten mit einer großen vertikalen Ausdehnung bis zur Oberfläche des Substrates können dazu dienen, in einem n-dotierten Substrat eine p-dotierte Wanne anzulegen, in der wiederum n-Kanal-Metall-Isolator-Halbleiter-Feldeffekttransistoren (n-Kanal-MISFET bzw. n-Kanal-MOSFET) angelegt werden können.

- Oberflächennahe Dotierungen können als Source-Drain-Region von Transistoren oder als Widerstandsbereiche genutzt werden.

- Dotierung in Randbereichen ist eines der Verfahren, mit dem sogenanntes gestrecktes Silizium realisiert werden kann – Bereiche mit erweiterter Gitterstruktur, in denen erhöhte Ladungsträgermobilität herrscht und in denen daher hochperformante Transistoren erstellt werden können.

Nach einer Implantation schließt sich immer ein Ofenprozess an (Temperung), um die implantierten Fremdatome, die sich auf Zwischengitterplätzen befinden, gleichmäßig in das Kristallgitter einzubauen und die im Kristallgitter entstandenen Schäden auszuheilen. (Das Kristallgitter des Substrats wird durch den Beschuss mit Ionen mechanisch geschädigt)

Abscheiden und Aufwachsen von Schichten

Schichten aus isolierenden und leitenden Materialien werden für viele Zwecke auf dem Halbleitersubstrat aufgebracht.

- Im Ofenprozess durch thermische Oxidation des Grundmaterials Silizium hergestellte Oxidschichten sind amorph und besitzen eine geringe Defektdichte (auch an den Grenzflächen), so dass sie als Dielektrikum für die Steuerelektroden der Feldeffekttransistoren, für Kondensatoren und die Bauelementisolation (vgl. LOCOS und Grabenisolation) benutzt werden.

- Aus der Gasphase abgeschiedene Oxide oder Nitride (chemische Gasphasenabscheidung, CVD) werden zum Beispiel als Isolation zwischen verschiedenen Bauelementen oder als Opferschichten für Ätzprozesse erzeugt.

- Durch physikalische Gasphasenabscheidung oder Sputtern können zum Beispiel Metallschichten aus Aluminium oder Kupfer aufgebracht werden, aus denen dann Leiterbahnen herausgeätzt werden können.

Strukturieren von Schichten

Um im Grundmaterial Bereiche zu entfernen oder aus abgeschiedenen Schichten bestimmte Bereiche herauszulösen werden Ätzverfahren eingesetzt. Man unterscheidet zwischen anisotropen (richtungsabhängig) und isotropen (richtungsunabhängig) Ätzverfahren.

- Das anisotrope Plasmaätzen (Trockenätzen, Reaktives Ionen Ätzen, RIE) ist der heute vorherrschende Prozess zur Strukturierung. Dabei wird das Material abgebaut, indem reaktive Ionen auf die Waferoberfläche beschleunigt werden – damit hat der Prozess eine mechanisch/physikalische und eine chemische Komponente.

- Die Bedeutung des nasschemischen Ätzens im Säurebad ist zurückgegangen, es wird heute vorwiegend zur Entfernung kompletter Schichten (Opferschichten) und zur Entfernung von Prozessrückständen verwendet.

- Zur Versiegelung der Chip-Oberfläche, d. h. zur Passivierung, wird meist ein Silikatglas abgeschieden. Dieses Silikatglas muss an den Bondflächen für die Außenkontaktierung entfernt werden. In dem Fall wird mittels Lithographie das Glas an den Bondflächen entfernt, hierbei wird oft Flusssäure als Ätzmittel verwendet. Die Flusssäure greift das Silikatglas an, während das reine Silizium unversehrt bleibt.

Planarisieren, Reinigen, Messen

Dadurch dass z. B. Leiterbahnen ein gewisses strukturelles Muster auf der Oberfläche des Substrates erzeugen, kommt es zu störenden Unebenheiten (z. B. Störung der Lithographie durch Schrägreflexion, Ungleichmäßigkeiten in folgenden Abscheidungen). Daher wird an mehreren Stellen im Fertigungsablauf der Wafer wieder planarisiert. Das kann durch selektives Zurückätzen oder durch chemisch-mechanisches Polieren (CMP) erfolgen.

Nicht nur das Polieren hinterlässt Partikel auf der Oberfläche, die für den nächsten Lithografieschritt völlig rein und eben sein muss. Auch z. B. Ätzprozesse hinterlassen Rückstände von unerwünschten Reaktionsprodukten. Im ersten Fall werden die Wafer mechanisch durch Bürsten und Ultraschallbad gereinigt, im zweiten Fall durch nasschemische Verfahren und ebenfalls Ultraschall.

Um die feinen Strukturen und dünnen Schichten mit Toleranzen von wenigen Nanometern zuverlässig erzeugen zu können, braucht man weiterhin sehr leistungsfähige Messverfahren zur Prozesskontrolle. Eingesetzt werden unter anderem diverse Spektroskopie- und Scatterometrie-Verfahren, Rasterkraftmikroskopie und diverse elektrische Messverfahren sowie Partikel- und Defektkontrollen zum Einsatz.

An die Produktionssteuerung werden erhebliche Ansprüche gestellt. Es liegt keine Fließfertigung vor, sondern eine so genannte Werkstattfertigung. Die Produktionsdauer für ein Los (üblicherweise 25 Wafer) in einer typischen Halbleiterfabrik (englisch: fab) bei kontinuierlicher Fertigung (7 Tage pro Woche, 24 Stunden pro Tag) liegt zwischen einigen Tagen und einigen Monaten, abhängig von der Komplexität des Produktes.

Halbleiterstrukturen

→ Hauptartikel: p-n-Übergang, Transistor

Durch die Abfolge der Einzelprozesse werden auf (bzw. in) dem Halbleitersubstrat Wannen unterschiedlicher Leitfähigkeit, Transistoren, Widerstände, Kondensatoren, Leiterbahnen und vieles mehr realisiert. Exemplarisch wird das Zusammenwirken der Prozesse an der Struktur eines Transistortyps erklärt.

Zur Herstellung einer Transistorebene auf einem Halbleitersubstrat ist eine Vielzahl der oben erklärten Prozessschritte notwendig. Nachfolgend soll kurz zusammengefasst die Prozessabläufe für die Herstellung heutiger (2009) Transistorstrukturen dargestellt werden:

- Noch vor der Erzeugung der eigentlichen Transistorstrukturen erfolgt die Herstellung von Isolationsstrukturen zwischen den späteren Transistoren; die dominierende Technik ist die Grabenisolation (engl. shallow trench isolation, vgl. Trench-Technik). Dazu werden zunächst fotolithografisch entsprechenden Bereiche zwischen den Transistorgebieten maskiert. Anschließend erfolgen eine Siliziumätzung (meist durch reaktives Ionenätzen) und die Wiederauffüllung mit Siliziumoxid sowie die Glättung der Topographie mithilfe des chemisch-mechanischen Polieres.

- Auf den verbleibenden Siliziuminseln wird in einem Ofen eine dünne Siliziumoxidschicht aufgewachsen – das spätere Gate-Dielektrikum des Transistors.

- Auf der gesamten Wafer-Oberfläche wird das Material für die Gateelektrode abgeschieden – in der Regel ein Stapel aus mehreren Materialien, z. B. hochdotiertes Silizium, Metall und Isolationskappe.

- Mit einem Lithografieschritt werden die Strukturen der Gate-Elektroden definiert, dann wird das Gate-Elektrodenmaterial überall dort weggeätzt, wo kein Fotolack nach der Entwicklung mehr übrig war.

- In einem Ofenprozess wird an den nun offenen Flanken der Gate-Strukturen ein Oxid zur Isolation und als Abstandshalter für die Folgeprozesse gebildet.

- Mittels Lithografie werden erst die n-Kanal-MOSFET-Transistorgebiete, dann die p-Kanal-Transistorgebiete abgedeckt, um jeweils die Source-Drain-Gebiete mit den richtigen Fremdatomen zu dotieren (Ionenimplantation).

- Um die Transistorebene gegen die folgenden Verdrahtungsebenen abzuschließen wird eine dicke Isolationsschicht auf dem gesamten Wafer aufgetragen. Überall dort, wo die Gates-Strukturen sind, bilden sich Buckel in der Isolationsschicht, die durch chemisch-mechanisches Polieren entfernt werden müssen.

Der heute übliche Fertigungsablauf für Transistoren enthält noch eine Vielzahl weiterer Prozesse, z. B. diverse Hilfsdotierungen oder dickere Gate-Dielektrika für Dickoxidtransistoren.

Status und Ausblick

In weniger als einem Jahrzehnt hat sich Halbleitertechnik zur Schlüsseltechnologie des 20. Jahrhunderts entwickelt. Der Kalte Krieg und die daraus resultierenden militär- und informationstechnischen Bedürfnisse waren Geburtshelfer, Katalysator und sind bis heute entscheidende Triebfeder der Entwicklung (siehe z. B. neuste Entwicklungen in der Prozessortechnik, Datenspeicherung, Signalverarbeitung, Optoelektronik etc.). Der Aufbau eines stabilen produktionstechnologischen Gerüsts wurde erst durch die kommerzielle Fertigung mikroelektronischer Schaltungen im großindustriellen Maßstab, z. B. für die ersten Taschenrechner, erzwungen.

Die Rolle des technologischen Vorreiters, den die Halbleitertechnik über Jahrzehnte innehatte, beginnt langsam zu verblassen. Andere Technologien wie die Biotechnologie haben begonnen, die Staffelstab zu übernehmen. Die Halbleitertechnik befindet sich heute im Übergang von einer jungen Technologie zu einer gereiften und sich konsolidierenden Technologie (Technologielebenszyklus). In Zukunft werden in erster Linie kleine, aus rein technischer Sicht durchaus herausfordernde Innovationsschritte und evolutionäre Detailverbesserungen die Szene bestimmen. Das Ziel ist und wird es sein, die Möglichkeiten der bestehenden Techniken auszuschöpfen. Größere Entwicklungssprünge, ohnehin bei großtechnischen Produktionstechniken kaum zu erwarten, werden bei Halbleitertechniken unwahrscheinlicher. Dies gilt zumindest für die Industriezweige, die sich der Herstellung von integrierten Schaltkreisen widmen. Andere Teilbereiche der Mikroelektronik wie Bildschirme oder Solarzellen, weisen weiterhin ein großes Forschungspotential auf.

Die Forschung und Technologieentwicklung für die Herstellung von integrierten Schaltkreisen erfolgt daher entlang sogenannter Roadmaps (dt.: »Projektplan«). Die maßgebende Roadmap ist die seit 1988 existierende ITRS (International Technology Roadmap for Semiconductors), die mitwirkenden Firmen machen mehr als 90 % weltweiten Halbleiterproduktion aus. In der ITRS werden die langfristigen Entwicklungsziele der Halbleiterindustrie auf 15 Jahre im Voraus geplant und regelmäßig der aktuellen Entwicklung angepasst. Die Entwicklungsstufen oder -schwerpunkte (engl. nodes) werden über den Begriff der Strukturgröße definiert. Die gebündelte Richtungsvorgabe bei der Entwicklung soll technologische Engpässe früh erkennen und Forschungsanreize setzen. Dadurch ist es der Industrie bis heute gelungen das bekannte mooresche Gesetz aufrechtzuerhalten. Wann das zu erwartende Abknicken oder Abbrechen der mooreschen Geraden und damit das Ende der stetig-evolutionären Entwicklung beginnt, bleibt abzuwarten. Da die Produktion aber heutzutage in Bereichen arbeitet, die vor 20 Jahren als physikalisch „unmöglich“ galten, ist zu erwarten, dass sich das Ende dieser Entwicklung um weitere Jahre verschiebt. Das Ende ist aber spätestens bei Fertigung von Bauelementen mit Strukturgrößen (< 10 nm) von wenigen Atomen auf Basis der heutigen siliziumorientierten Technologie erreicht. Hier sind neue Entwicklungen mit neuartigen Funktionsweisen notwendig um den Trend des mooreschen Gesetzes zu folgen. Die ITRS beschäftigt sich im Kapitel „Emerging Research Devices“ (ERD) zunehmend intensiver mit potentiellen Technologien, die allerdings immer noch stark an der bestehenden Technologie angelehnt sind. Dazu gehören neben technologisch verwandten Konzepten wie dem FeRAM oder geschichtete Dielektrika (beispielsweise engineered tunnel barrier memory) auch Konzepte, die wohl nicht in den nächsten zehn Jahren anwendungsreif werden, wie Speicher und Schaltkreise auf Basis von leitenden Makromolekülen oder Einzelelektronentransistoren.

Wie andere Spitzentechnologien verursacht auch die Halbleitertechnologie stetig steigenden Kosten, um die Weiterentwicklung der existierenden Technologie aufrecht zu erhalten, vor allem im Bereich der Schaltkreisherstellung. Kostentreibend ist neben dem hohen finanziellen Aufwand für Anlagentechnik und die ebenso aufwendige, komplexe Fertigung die Arbeitsweise in Forschung und Entwicklung. Die empirische Entwicklungsarbeit ist in vielen Bereichen immer noch notwendig, da entsprechende Simulationen die Vorgänge noch nicht mit der geforderten Genauigkeit wiedergeben. Dies liegt zum einen an den sehr hohen Toleranzanforderungen als auch an fehlenden physikalischen Erklärungen für die Vorgänge im Nanometerbereich, dies betrifft beispielsweise das chemisch-mechanische Polieren oder den exakten Ablauf des Beschichtungsprozesses bei der Atomlagenabscheidung. Wie in anderen technischen Disziplinen wird aber auch in der Halbleitertechnologie verstärkt an der Simulation von Prozessabläufen gearbeitet und vielfältig eingesetzt. Neben den seit Jahrzehnten eingesetzten Simulationen bei der Entwicklung und Verifizierungen von Schaltkreisen, werden auch zunehmend komplette Produktionsabläufe der Halbleiterbauelemente simuliert.

Polykristalline Silizium-Solarzellen in einem Solarmodul

Polykristalline Silizium-Solarzellen in einem Solarmodul

In der Photovoltaik kommen neben den Entwicklungskosten noch die vergleichsweise hohen Modulpreise für den Endkunden hinzu. Hier war lange Zeit ein hoher Subventionsbedarf notwendig, um eine kostendeckende Forschung betreiben zu können und gleichzeitig attraktive Produktpreise anzubieten, um die Technologie gegen konventionelle Kraftwerke (Kohle, Gas usw.) aufzustellen. Ziel dieser Politik, vor allem in Deutschland, war damals wie heute die Förderung alternativer und regenerativer Energiekonzepte. Derzeit (2008) wird dieser Bereich immer noch stark subventioniert – was unter anderem an der Vielzahl von Neugründungen vor allem in den östlichen Bundesländern zu sehen ist –, obwohl der Photovoltaikmarkt seit einigen Jahren weltweit boomt.

Siehe auch: Das moorsche Gesetz – Technische Grenzen

Umweltschutz

Zu Beginn der Massenfertigung von Halbleiterbauelementen wurde den Umweltschutzaspekten recht wenig Beachtung geschenkt. Vor allem im Silicon Valley kam es in den späten 1960er- und frühen 1970er-Jahren zu großflächigen Grundwasserverschmutzungen. Diese Vorfälle brachten erstmalig die Kehrseite einer bislang als besonders fortschrittlich geltenden Industrie zum Vorschein.

In der Tat werden im Zusammenhang mit der Herstellung mikroelektronischer Bauelemente umweltgefährdende Substanzen produziert, eingesetzt und emittiert. Hierzu zählen u. a. zahlreiche Schwer- und Halbmetalle, ozonschichtzerstörende Substanzen und Treibhausgase. Rückstände fallen – ggf. in umgewandelter und vermischter Form – als Feststoffe, Flüssigkeiten und Gase an. Viele der Einsatzstoffe werden aus technischen oder ökonomischen Gründen nicht recycled.

Seit Mitte der 1980er-Jahre traten in vielen Industrieländern gesetzliche Regeln in Kraft, die die Industrie veranlasst haben, Maßnahmen zur lokalen Reduzierung des Umweltgefährdungspotentials zu implementieren. In den Boomregionen Asiens werden Umweltschutzaspekte jedoch oft ökonomischen Interessen untergeordnet. Freiwillige Regularien wie die seit Mitte der 1990er-Jahre einsetzende internationale Standardisierung z. B. nach ISO 14001 (Environmental Management Systems) greifen dort naturgemäß wenig, solange sie nicht von nationalem Recht unterstützt werden.

Literatur

- Ulrich Hilleringmann: Silizium-Halbleitertechnologie: Grundlagen mikroelektronischer Integrationstechnik. 5. Auflage. Vieweg+Teubner, 2008, ISBN 3-8351-0245-1.

- Dietrich Widmann, Hermann Mader, Hans Friedrich: Technologie hochintegrierter Schaltungen. 2. Auflage. Springer, Berlin 1996, ISBN 3-540-59357-8.

Weblinks

- www.halbleiter.org – Grundlagen der Halbleitertechnologie

Wikimedia Foundation.